今天小编要和大家分享的是MEMS,传感技术相关信息,接下来我将从硅3D集成技术全面解析,gmy400w矿用本安型无线锚杆(索)应力传感器这几个方面来介绍。

MEMS,传感技术相关技术文章硅3D集成技术全面解析

从低密度的后通孔TSV硅3D集成技术,到高密度的引线混合键合或3D VSLI CoolCubeTM解决方案,研究人员发现许多开发新产品的机会。本文概述了当前新兴的硅3D集成技术,讨论了图像传感器、光子器件、MEMS、Wide I/O存储器和布局先进逻辑电路的硅中介层,围绕3D平台性能评估,重点介绍硅3D封装的主要挑战和技术发展。

硅的3D应用机会

从最初为图像传感器设计的硅2.5D集成技术,到复杂的高密度的高性能3D系统,硅3D集成是在同一芯片上集成所有功能的系统芯片(SoC)之外的另一种支持各种类型的应用的解决方案,可用于创建性价比更高的系统。硅3D集成技术的主要优势:缩短互连线长度,降低R.C积,让先进系统芯片(SoC)能够垂直划分功能,进一步降低系统尺寸和外形因数。

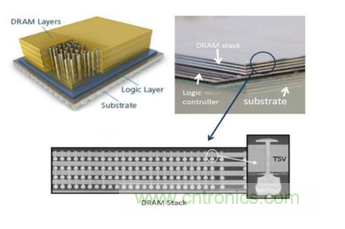

在首批出现的3D产品中,业界认为存储器层叠方案可以提高DRAM/逻辑控制器的容量/带宽,适用于高性能计算系统、图形处理器、服务器和微型服务器(图1)。

图1:与逻辑控制器相连的DRAM混合存储器层叠模块(HMC)。

美光的混合存储器模块(HMC)和海力士的宽带存储器(HBM)开始进入量产阶段,这两个解决方案都连接硅中介层,面向高性能计算(HPC)应用。

Xilinx于2012年提出在硅中介层制造现场可编程门阵列(FPGA)的概念,该技术最初采用CoWoS集成工艺,引起供应链巨变,后来改用两个28nm FPGA和两个65nm混合信号芯片堆叠在65nm中介层上。

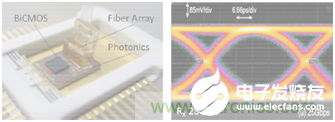

服务器对高带宽和低功耗的进一步需求催生了将CMOS/BiCMOS和光子功能分开的每个通道传输速率高达25Gb/s的硅光子器件平台(图2),以及产生了硅光中介层集成技术。

图2左图:一个采用3D层叠技术在光子器件上安装BiCMOS器件的光学封装测试芯片;右图:该芯片在RX 25/28Gbps时的电眼测量图

研究人员认为在逻辑层上堆叠存储层可以大幅降低存储器与处理器之间的接口功耗。堆叠在逻辑层上的Wide I/O DRAM(图3)的能效是LPDDR解决方案的四倍,并且在未来几年内传输速率将达到50GB/s。