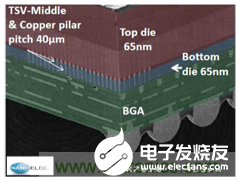

图3:置于65nm逻辑层上的Wide IO存储器,顶层/底层具有1250个TSV互连线,1000个倒装片铜柱(底部/BGA)。

为了给高性能计算或电信应用提供高带宽性能,研究人员设计了一个基于异步3D Network-On-Chip架构的先进逻辑层叠方案,采用3D封装方法将两颗相同的逻辑裸片正反面层叠,证明了可扩展的同构3D层叠方法的技术优势。该3D集成方案的逻辑芯片采用CMOS 65nm制造工艺,使用宽高比为1:8的TSV Middle通孔和40μm节距的铜柱连接芯片(图4)。

图4:采用逻辑芯片层叠方法的异步Network-on-Chip 3D架构

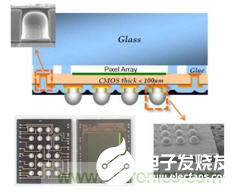

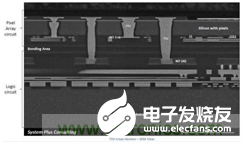

在2.5D TSV被引入CMOS图像传感器(图5)后,3D集成技术从2013年开始进入智能手机和平板电脑中,目前市场上存在多个不同的相互竞争的层叠技术,数字处理层可以布局在硅衬底上,而不是像素阵列电路上,通过功能划分和工序优化,图像传感器尺寸变得更加紧凑(图6)。

图5:晶圆级摄像头2.5D后通孔方法。

图6:索尼图像传感器采用直接键合+TSV的晶圆级层叠解决方案(来源:System Plus Consulting)。

对于MEMS,微缩化是除成本和性能之外的另一个差异化要素。2007年以来,技术发展趋势是开发3D异构MEMS功能,包括通过TSV连接IC(图7)。

图7:博世采用TSV 3D技术在ASIC中集成3轴加速度计(来源:Yole Developpement)。

3D技术挑战

3D集成被广泛应用证明,TSV等先进技术节点的基本模块技术已经成熟(图8)。现在,研发重点转移到由市场需求驱动的新挑战上:封装应变管理;通过改进散热效率提高系统性能;提高芯片间的互连密度。

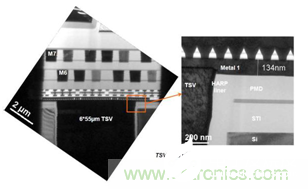

图8:6x55µm 28FDSOI Via Middle集成TEM视图,对测试载具良率没有影响,通过了TDDB、EMG和TC测试

对于较大的硅中介层来说,热机械应变是一个需要考虑的难题,需要解决硅光子变化以及HBM/CPU集成封装问题,叠层之间的热膨胀系数(CTE)不匹配将会致使裸片翘曲。根据裸片级曲率对温度的敏感性,研究人员开发出一种应变监测和翘曲补偿策略,通过综合使用阴影莫尔干涉仪(图9)、现场应力传感器和有限元建模(FEM)方法,创建了介电层特性模型。(图10)