今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从VHDL概述及在描述数字电路时的结构,数字万用表电路图dt9208a型号这几个方面来介绍。

EDA,IC设计相关技术文章VHDL概述及在描述数字电路时的结构

本文介绍了一种硬件描述语言VHDL,以及它在描述数字电路时的结构。我们还将介绍一些介绍性的示例电路描述,并讨论“std_logical”和“bit”数据类型之间的区别。

VHDL是数字电路设计中常用的硬件描述语言之一。VHDL代表VHSIC硬件描述语言。反过来,VHSIC代表超高速集成电路。

VHDL是1981年由美国国防部发起的。IBM和德州仪器等公司的合作导致VHDL于1985年发布了第一个版本。1984年,Xilinx发明了第一个FPGA,很快就在其产品中支持VHDL。从那时起,VHDL语言在数字电路设计、仿真和综合方面已经发展成为一种成熟的语言。

在本文中,我们将简要讨论描述给定电路的VHDL代码的一般结构。通过一些介绍性示例,我们还将熟悉一些常用的数据类型、操作符等。

VHDL的一般结构

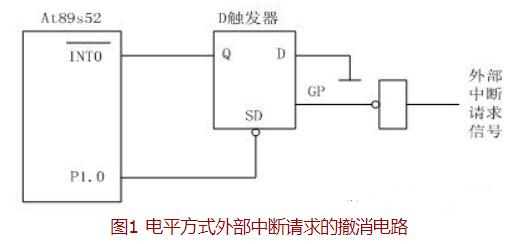

让我们考虑一个简单的数字电路,如图1所示。

图1.一个简单的数字电路。

此图显示有两个输入端口,a和b,以及输出端口out 1。图中显示输入和输出端口有一点宽。电路的功能是要和两个输入端,并将结果放在输出端口上。

VHDL使用类似的描述;但是,它有自己的语法。例如,它使用以下代码行来描述该电路的输入和输出端口:

1 entity circuit_1 is 2 Port ( a : in STD_LOGIC; 3 b : in STD_LOGIC; 4

out1 : out STD_LOGIC); 5 end circuit_1;

让我们分清这意味着什么,一行行。

第1行:代码的第一行指定要描述的电路的任意名称。在关键字“实体”和“is”之间的“电路1”一词决定了该模块的名称。

第2至第4行:这些线路指定电路的输入和输出端口。将这些线路与图1中的电路进行比较,我们发现该电路的端口及其特性列在关键字“port”之后。例如,第3行说我们有一个名为“b”的端口。此端口是一个输入,如冒号后面的关键字“in”所示。

关键字“std_Logic”指定了什么?正如我们将在本文后面讨论的那样,std_Logic是VHDL中一种常用的数据类型。它可以用来描述一位数字信号。由于图1中的所有输入/输出端口都将传输1或0,因此我们可以对这些端口使用std_logicdata类型。