今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从如何解决PCB板的电镀夹膜问题,pcb 线路板这几个方面来介绍。

EDA,IC设计相关技术文章如何解决PCB板的电镀夹膜问题

一、前言:

随着PCB行业迅速发展,PCB逐渐迈向高精密细线路、小孔径、高纵横比(6:1-10:1)方向发展,孔铜要求20-25Um,其中DF线距≤4mil之板,一般生产PCB公司都存在电镀夹膜问题。夹膜会造成直接短路,影响PCB板过AOI检查的一次良率,严重夹膜或点数多不能修理直接导致报废。

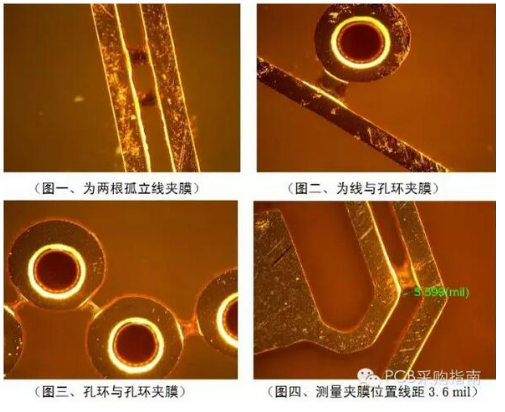

二、图形电镀夹膜问题图解说明:

PCB板夹膜原理分析

① 图形电镀线路铜厚大于干膜厚度会造成夹膜。(一般PCB厂所用干膜厚度1.4mil)

② 图形电镀线路铜厚加锡厚超过干膜厚度可能会造成夹膜。

三、PCB板夹膜原因分析

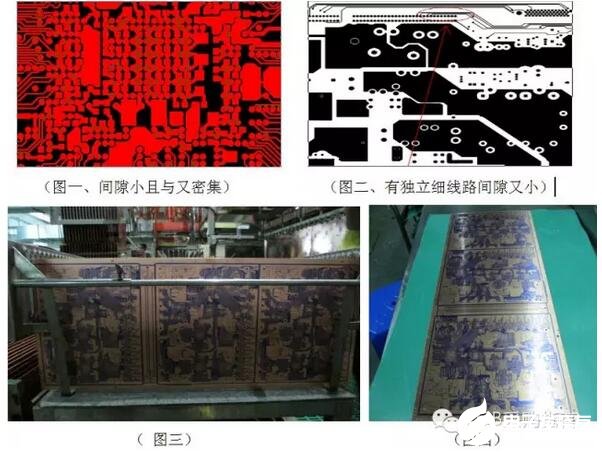

1.易夹膜板图片及照片

图三与图四,从实物板照片可看出线路较密集,工程设计排版长宽比例相差较大不利电流分布, D/F最小线隙为2.8mil(0.070mm),最小孔为0.25mm,板厚:2.0mm, 纵横比8:1,孔铜要求>20Um以上。属于制程难度板。

2.夹膜原因分析

①图形电镀电流密度大,镀铜过厚。

②飞巴两端未夹边条,高电流区镀厚夹膜。

③火牛故障比实际生产板设定电流大。

④C/S面与S/S面挂反。

⑤间距太小2.5-3.5mil间距之板夹膜。

⑥电流分布不均匀,镀铜缸长时间未清洗阳极。

⑦打错电流(输错型号或输板子错面积)

⑧设备故障坏机PCB板在铜缸保护电流时间太长。

⑨工程排版设计不合理,工程提供图形有效电镀面积有误等。

⑩PCB板线隙太小,高难度板线路图形特殊易夹膜。

四、夹膜有效改善方案

1、降低图电电流密度,适当延长镀铜时间。

2、把板电镀铜厚适当加厚,适当降低图电镀铜密度,相对减少图形电镀铜厚度。

3、压板底铜厚由0.5OZ改为1/3OZ底铜压板。把板电镀铜厚加厚10Um左右,降低图电电流密度,减少图形电镀铜厚度。

4、针对间距<4mil之板采购1.8-2.0mil干膜试用生产。