在板级高速PCB仿真过程中主要用要的模型有器件模型和传输线模型。器件模型一般是由器件生产厂家提供的。在高速串行信号中,我们采用的是精度更高的SPICE模型来进行仿真分析。传输线模型则是通过仿真软件建模形成的。信号在传输时,传输线会使得信号完整性问题突出,因此仿真软件对传输线精确建模的能力直接影响仿真结果。

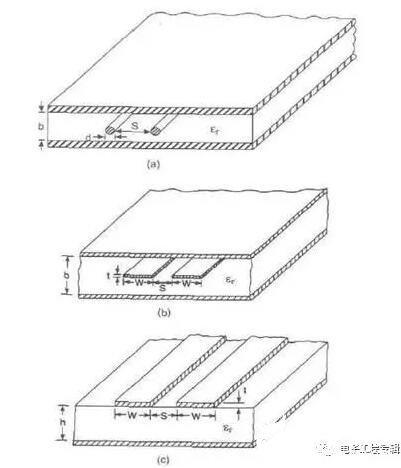

图3:差分对线模型b:带状线 c: 微带线而信号路径和返回路径所在的传输线不可能是理想的导体,因此它们都有有限的电阻,电阻的大小由传输线的长度和横截面积决定。任何传输线都可以划分为一系列串接线段。同样的在传输线之间的介质也不可能是理想的绝缘体,漏电流总是存在的。实际的传输线模型由无数个短线段组成,短线段的长度趋于零。 关于传输线的模型是allegro自动分配的。仿真的时候主要是分配器件模型。

3.5.SI检查

SI Audit功能是用来检查某一个特殊的网络或者一群网络是否能够被提取出来进行分析,一般就是设置我们需要关注的高速网络,本设计主要关注LVDS串行信号。

3.6.提取网络拓扑

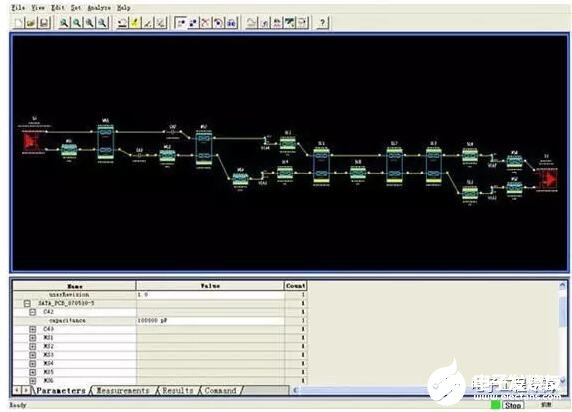

从PCB中提取待关注信号的拓扑结构,一般包括驱动端和接收端,以及传输线和相关的匹配电阻电容等,可以从拓扑结构中看出该网络经过那些路径,那些会对信号的传输造成影响。本文仅以其中一个信号的网络拓扑图为例:如图4所示:

图4 差分对线的网络拓扑

3.7.查看波形

以上的相关步骤设置好以后就可以进行仿真了,allegro可以进行信号的反射仿真、串扰仿真,差分线还要进行眼图分析。当然仿真也分前仿真和后仿真,在利用allegro进行PCB设计的时候还需要结合仿真的结果实时的对设计进行修改以达到符合要求的目的。由于仿真过程复杂,步骤繁琐,在此不一一进行描述, 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,等长是为了保证两个差分信号时刻保持相反极性,减少共模分量。另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者side-by-side 实现的方式较多。等距则主要是为了保证两者差分阻抗一致,减少反射。对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。从仿真的S参数曲线图可以分析差分对的差分阻抗(differential impedance),以及信号完整性。下面给出本设计中的关键信号仿真波形以供加以说明。 从仿真图例图5看到,S11在0-3.0GHz 的频域范围内其最劣化的指标为:-16.770db以下 ,S22(粉红色的曲线)也不劣于-17db。 这说明该差分对的差分阻抗(differential impedance)接近设计指标,信号完整性得到了保证。