其它节点就不是如此关键了。所以不必忧虑开关节点、二极管、COUT、开关IC的VIN接脚或CIN。

布线技巧

布线手法会为电阻分压器带来差别。该导线从COUT连至电阻分压器,其接地回到COUT。我们必须确保该回路不会形成一个开放区域。开放区域会产生接收天线的作用。若我们能保证导线下的地平面是没被干扰的,则由导线和其下的接地以及level1和level2间形成的区域应是不受干扰的。现在,我们可得知为何接地不应放在level4,因为距离显着增加了。

另一种方式是电阻分压器的地连接可布线至level1,使两条导线平行并尽可能靠近以使区域更小。这些观察适用于讯号流经的全部导线:传感器连接、放大器输出、ADC或音讯功率放大器的输入。对每个模拟讯号,都要处理得使其不太容易导入噪声。

只要有可能,就尽量最小化开放区域的这个要求,对低阻抗导线也同样适用;在这种情况下,我们有一个向PCB其它部份或其它设备发射干扰讯号的潜在源(天线)。注意:就开放区域来说是越小越好。

以下两条导线也很关键:从IC的开关输出到二极管和电感节点;从二极管到该节点。这两条导线都有很高的di/dt:无论是开关导通还是二极管流过电流,所以导线应尽可能短而粗。从节点到电感以及从电感到COUT的导线就不那么关键。在本例中,电感电流相对恒定且变化缓慢。我们要做的是确保它是低阻抗点以最小化压降。

实际布局

我们看一下好的布局(下面)。主要组件是一款与外接FET一起使用的MSOP-8封装控制器。

观察CIN附近的空间。注意:该电容的接地点直接连至二极管阳极。你无法使‘电源地’内的导线过短!FET[SW]应向上移动几毫米以缩短阴极-电感-FET导线。

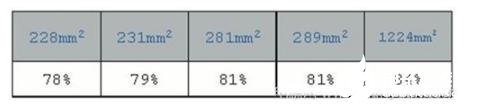

COUT区域是看不到的。但我们可观察到电阻分压器(FB1-FB2)非常接近该IC。FB2与另一个地平面连接,IC的地接脚也一样处理。利用三个过孔把‘讯号’地连至地平面,而‘电源’地也是利用三个过孔连接PCB的GND接脚。这样,‘讯号’地就不会‘看’到‘电源’地的任何接地弹跳。

若你遵循几个简单规则(本文仅讨论了其中一些),则你的PCB布局将不会遇到麻烦。在动手布局前,仔细思考PCB布局将事半功倍,有助于节省处理开关电源异常所需花费的时间。

责任编辑;zl

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。