对于一些高性能的芯片,无论内核或是IO的电源供电都集成了很多去耦单元。集成电路封装结构,如同一个缩小了的PCB,有几层形状复杂的电源或地平板。在封装结构的上表面,通常留有去耦电容的安装位置。PCB则通常含有连续的面积较大的电源和地平板,以及一些大大小小的分立去耦电容元件,及电源整流模块(VRM)。邦定线、C4凸点、焊球则把芯片、封装和PCB连接在了一起。

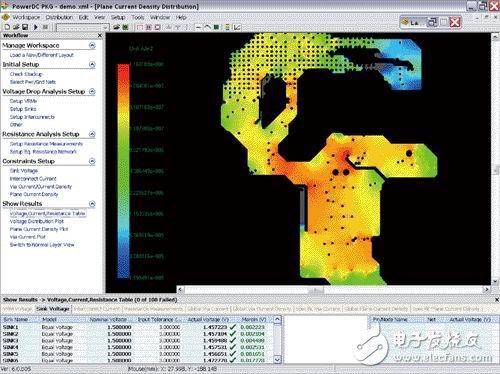

整个电源供电系统要保证给各个集成电路器件提供在正常范围内稳定的电压。然而,开关电流和那些电源供电系统中寄生的高频效应总是会引入电压噪声。其电压变化可以由下式计算得到:

这里ΔV是在器件处观测到的电压波动,ΔI是开关电流。Z是在器件处观测到的整个电源供电系统电源与地之间的输入阻抗。为了减小电压波动,电源与地之间要保持低阻。在直流情况下,由于Z变成了纯电阻,低阻就对应了低的电源供电IR压降。在交流情况下,低阻能使开关电流产生的瞬态噪声也变小。当然,这就需要Z在很宽的频带上都要保持很小。

这里ΔV是在器件处观测到的电压波动,ΔI是开关电流。Z是在器件处观测到的整个电源供电系统电源与地之间的输入阻抗。为了减小电压波动,电源与地之间要保持低阻。在直流情况下,由于Z变成了纯电阻,低阻就对应了低的电源供电IR压降。在交流情况下,低阻能使开关电流产生的瞬态噪声也变小。当然,这就需要Z在很宽的频带上都要保持很小。

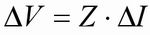

图2:Sigrity PowerDC计算得到电源板层上的电流分布。注意到电源和地通常用来作为信号回路和参考平面,因此电源供电系统与信号分布系统之间有着很紧密的关系。然而,由于篇幅的限制,同步开关噪声(IO SSO)引入的电源供电系统的噪声现象和电流回路控制问题将不在这里讨论。以下几节将忽略信号系统,而单纯注重电源供电系统的分析。

直流IR压降

由于芯片的电源栅格(Power Grid)的特征尺寸很小(几微米甚至更小),芯片内的电阻损耗严重,因此芯片内的IR压降已经被广泛地研究。而在下面几种情况下,PCB上的IR压降(在几十到几百毫伏的范围内)对高速系统设计同样会有较大的影响。

电源板层上有Swiss-Chess结构、Neck-Down结构和动态布线造成的板平面被分割等情况(图1);电源板层上电流通过的器件管脚、过孔、焊球、C4凸点的数量不够,电源平板厚度不足,电流通路不均衡等;系统设计需要低电压、大电流,又有较紧的电压浮动的范围。

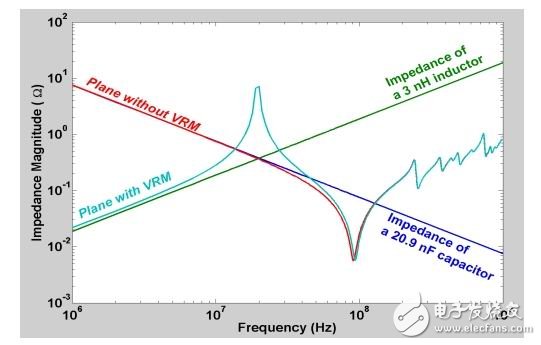

图3:包括和不包括电源整流模块的平板对输入阻抗。例如,一个高密度和高管脚数的器件由于有大量的过孔和反焊盘,在芯片封装结构及PCB的电源分配层上往往会形成所谓的Swiss-Chess结构效应。Swiss-Chess结构会产生很多高阻性的微小金属区域。根据