11.4.3 内电层分割基本原则

在完成内电层的分割之后,本节再介绍几个在内电层分割时需要注意的问题。

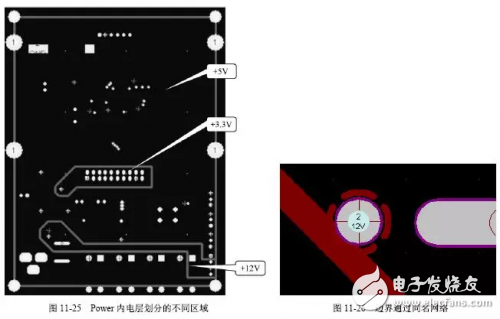

(1)在同一个内电层中绘制不同的网络区域边界时,这些区域的边界线可以相互重合,这也是通常采用的方法。因为在 PCB 板的制作过程中,边界是铜膜需要被腐蚀的部分,也就是说,一条绝缘间隙将不同网络标号的铜膜给分割开来了,如图 11-25 所示。这样既能充分利用内电层的铜膜区域,也不会造成电气隔离冲突。

(2)在绘制边界时,尽量不要让边界线通过所要连接到的区域的焊盘,如图 11-26 所示。由于边界是在 PCB 板的制作过程中需要被腐蚀的铜膜部分,有可能出现因为制作工艺的原因导致焊盘与内电层连接出现问题。所以在 PCB 设计时要尽量保证边界不通过具有相同网络名称的焊盘。

(3)在绘制内电层边界时,如果由于客观原因无法将同一网络的所有焊盘都包含在内,那么也可以通过信号层走线的方式将这些焊盘连接起来。但是在多层板的实际应用中,应该尽量避免这种情况的出现。因为如果采用信号层走线的方式将这些焊盘与内电层连接,就相当于将一个较大的电阻(信号层走线电阻)和较小的电阻(内电层铜膜电阻)串联,而采用多层板的重要优势就在于通过大面积铜膜连接电源和地的方式来有效减小线路阻抗,减小 PCB 接地电阻导致的地电位偏移,提高抗干扰性能。所以在实际设计中,应该尽量避免通过导线连接电源网络。

(4)将地网络和电源网络分布在不同的内电层层面中,以起到较好的电气隔离和抗干扰的效果。

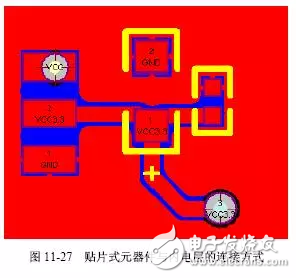

(5)对于贴片式元器件,可以在引脚处放置焊盘或过孔来连接到内电层,也可以从引脚处引出一段很短的导线(引线应该尽量粗短,以减小线路阻抗),并且在导线的末端放置焊盘和过孔来连接,如图 11-27 所示。

(6)关于去耦电容的放置。前面提到在芯片的附近应该放置 0.01μF 的去耦电容,对于电源类的芯片,还应该放置 10F 或者更大的滤波电容来滤除电路中的高频干扰和纹波,并用尽可能短的导线连接到芯片的引脚上,再通过焊盘连接到内电层。

(7)如果不需要分割内电层,那么在内电层的属性对话框中直接选择连接到网络就可以了,不再需要内电层分割工具。

11.5 多层板设计原则汇总