电源轨迹共享增加了PDN的复杂度,同时在PCB上和die的位置处也增加了大量的噪声。对于多路的情况,设计电源的分配解决方法主要有两步:

1 低频解决方法

2 高频解决方法

在非常低频的时候,第一步确保VRM的大小是否适合处理各种电流的需要。

低频去耦一定要考虑清楚各种组合电源供电电流的情况。Bulk电容一定要选择能覆盖目标阻抗所覆盖的频段。做到精确的知道频率范围是有困难的,因为这有一个区域超过了阻抗曲线,这是在die上给定的电源区域,建立在自己的最大电流消耗上,而不是与其它路电流相关联的由同一个供电电源供电组合的电流消耗。对于设计,bulk电容去耦的频率范围估计是从DC到大约5~10MHz。

在共享多路电源的时候,通过PDN工具按照相似的方法使用这种设计方法,但是推荐你在最高的截止频率点去耦。对于单一和共享多路电源的去耦,这是成功实现单一PDN方法设计的流程。这种方法是合适于与电源路之间与相似电流要求的电源路设计的。但是,对于这种方法这有几个例外。

这个例子是电源共享在核心电源供电(Vcc)和PCI Express hard IP Block(VccHIP)电源供电。例外的原因是:

■VCC的电流会比VCCHIP的大很多。

■对比VCC和VCCHIP,VCC的BGA的过孔电感会比VCCHIP低很多。

■对比VCC和VCCHIP,VCC的截止频率会比VCCHIP低很多。

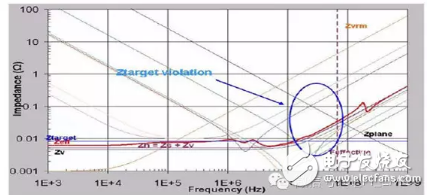

因此,对于电源设计情况,在BGA过孔处使用最高截止频率去耦是不适用的。如图3所示的是VCC、VCCHIP电源路组合阻抗曲线不符合目标阻抗的情况,相当于不符合VCCHIP的截止频率去耦。这是因为去耦电容效果被限制了

图3 VCCHIP的截止频率阻抗曲线

按照以前的解释,高频的噪声在电源轨迹中,主要是由于自己的瞬态电流产生的。对于共享电路最高截止频率的去耦设计指导书是基于整个瞬态电流的阻抗计算,这是“过设计”的要求。

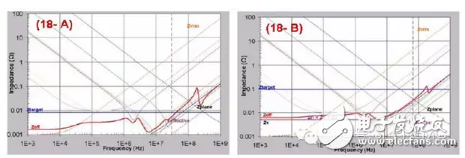

图4 更改电源路的共享情况

在这种情况下,你必须基于PCB去耦项目用整个瞬态电流来计算目标阻抗曲线,相当于电源路截止频率的最大的电流消耗。在VCC和VCCHIP电源路共享的例子中,你必须用VCC电源路的截止频率。如图3-A所示为核心电源去耦的截止频率的组合电源路的阻抗曲线。对于核心电源,用沿着BGA的球或者过孔的(VCC+VCCHIP)的总电流得到阻抗曲线。那么你可以检查核对结果是否符合单个电源设计指导的目标阻抗。