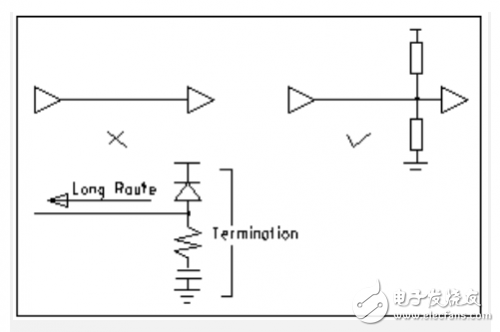

12、走线终结网络规则:

在高速数字电路中, 当PCB布线的延迟时间大于信号上升时间(或下降时间) 的1/4时,该布线即可以看成传输线,为了保证信号的输入和输出阻抗与传输线的阻抗正确匹配,可以采用多种形式的匹配方法, 所选择的匹配方法与网络的连接方式和布线的拓朴结构有关。

对于点对点(一个输出对应一个输入) 连接, 可以选择始端串联匹配或终端并联匹配。前者结构简单,成本低,但延迟较大。后者匹配效果好,但结构复杂,成本较高。

对于点对多点(一个输出对应多个输出) 连接, 当网络的拓朴结构为菊花链时,应选择终端并联匹配。当网络为星型结构时,可以参考点对点结构。星形和菊花链为两种基本的拓扑结构, 其他结构可看成基本结构的变形, 可采取一些灵活措施进行匹配。 在实际操作中要兼顾成本、 功耗和性能等因素, 一般不追求完全匹配,只要将失配引起的反射等干扰限制在可接受的范围即可。

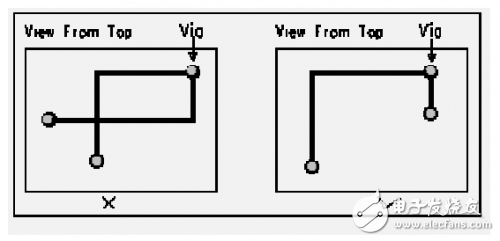

13、走线闭环检查规则:

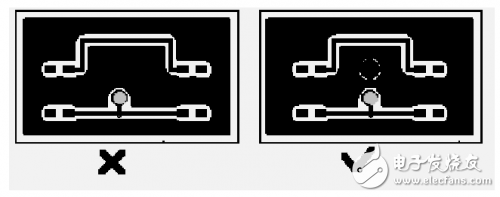

防止信号线在不同层间形成自环。 在多层板设计中容易发生此类问题, 自环将引起辐射干扰。

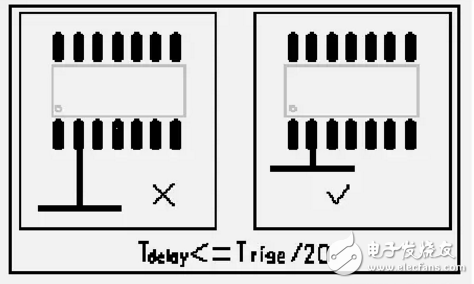

14、走线的分枝长度控制规则:

尽量控制分枝的长度,一般的要求是Tdelay<=Trise/20。

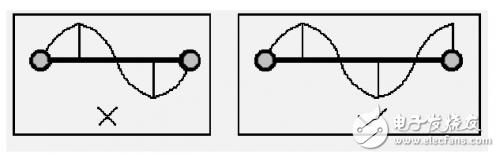

15、走线的谐振规则:

主要针对高频信号设计而言, 即布线长度不得与其波长成整数倍关系, 以免产生谐振现象。

16、孤立铜区控制规则:

孤立铜区的出现, 将带来一些不可预知的问题, 因此将孤立铜区与别的信号相接, 有助于改善信号质量,通常是将孤立铜区接地或删除。 在实际的制作中, PCB厂家将一些板的空置部分增加了一些铜箔,这主要是为了方便印制板加工,同时对防止印制板翘曲也有一定的作用。

17、重叠电源与地线层规则:

不同电源层在空间上要避免重叠。 主要是为了减少不同电源之间的干扰, 特别是一些电压相差很大的电源之间, 电源平面的重叠问题一定要设法避免, 难以避免时可考虑中间隔地层。