底板PCB的叠层为下图所示:

第二层为地平面,第五层为电源平面,其余各层为信号层。

各层的层厚如下表所示:

| Layer Name | Type | Material | Thinkness | Class |

| SURFACE | AIR | |||

| TOP | CONDUCTOR | COPPER | 0.5 OZ | ROUTING |

| DIELECTRIC | FR-4 | 3.800MIL | ||

| L2-INNER | CONDUCTOR | COPPER | 1 OZ | PLANE |

| DIELECTRIC | FR-4 | 5.910MIL | ||

| L3-INNER | CONDUCTOR | COPPER | 1 OZ | ROUTING |

| DIELECTRIC | FR-4 | 33.O8MIL | ||

| L4-INNER | CONDUCTOR | COPPER | 1 OZ | ROUTING |

| DIELECTRIC | FR-4 | 5.910MIL | ||

| L5-INNER | CONDUCTOR | COPPER | 1 OZ | PLANE |

| DIELECTRIC | FR-4 | 3.800MIL | ||

| BOTTOM | CONDUCTOR | COPPER | 0.5 OZ | ROUTING |

| SURFACE | AIR |

说明:中间各层间的电介质为FR-4,其介电常数为4.2;顶层和底层为裸层,直接与空气接触,空气的介电常数为1。

需要进行阻抗控制的信号为:

DDR的数据线,单端阻抗为50欧姆,走线层为TOP和L2、L3层,走线宽度为5mil。

时钟信号CLK和USB数据线,差分阻抗控制在100欧姆,走线层为L2、L3层,走线宽度为6mil,走线间距为6mil。

对于计算精度的说明:

1、对于单端阻抗控制,计算值等于客户要求值;

2、对于其他特性阻抗控制:

对于其它所有的阻抗设计(包括差别和特性阻抗)

*计算值与名义值差别应小于的阻抗范围的10%:

例如:客户要求:60+/-10%ohm

阻抗范围=上限66-下限54=12ohms

阻抗范围的10%=12X10%=1.2ohms

计算值必须在红框范围内。其余情况类推。

下面利用SI9000计算是否达到阻抗控制的要求:

首先计算DDR数据线的单端阻抗控制:

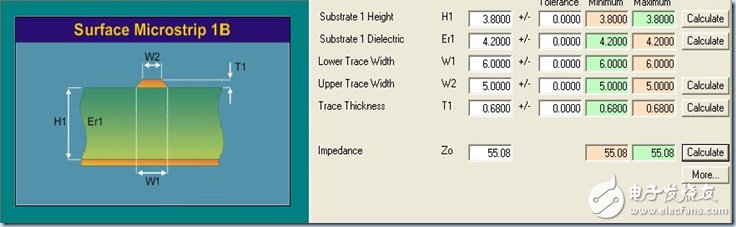

TOP层:铜厚为0.5OZ,走线宽度为5MIL,距参考平面的距离为3.8MIL,介电常数为4.2。选择模型,代入参数,选择lossless calculation,如图所示: