计算得到单端阻抗为Zo=55.08ohm,与要求相差5欧姆。根据板厂的反馈,他们将走线宽度改为6MIL以达到阻抗控制,经过验证,在宽度W2=6MIL,W1=7MIL的情况下,计算得到的单端阻抗为Zo=50.56欧姆,符合设计要求。

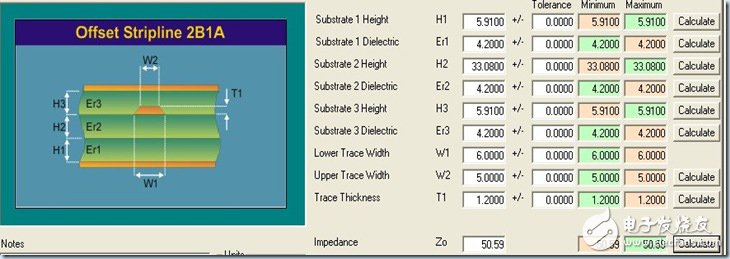

L2层:在L2层的走线模型如下图所示:

代入参数进行计算得到如下图所示:

计算得到单端阻抗为Zo=50.59欧姆,符合设计要求。

同理可以得到L3层的单端阻抗,在此不再赘述。

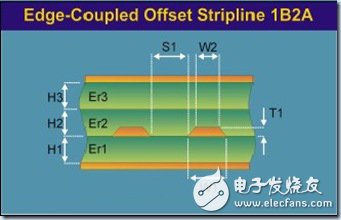

下面计算差分阻抗控制:

由PCB设计可知,底板PCB中时钟走线在L3层,USB数据线在L2层,走线宽度均为6MIL,间距为6MIL。

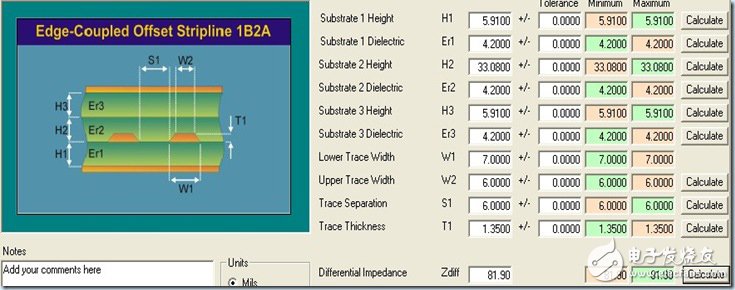

时钟信号选择的模型如下所示:

按照提供给板厂的数据计算得到的结果如下图所示:

根据板厂的反馈,差分阻抗只能做到85欧姆,与计算结果接近(他们可以微调板层厚度,但不能调线)。但是改变线间距为12MIL时,计算得到的差分阻抗为92.97欧姆,再将线宽调为5MIL时,差分阻抗为98.99欧姆,基本符合设计要求。

经验小结

1、当差分走线在中间信号层走线时,差分阻抗的控制比较困难,因为精度不够,就是说改变介质层厚度对差分阻抗的影响不大,只有改变走线的间距才对差分阻抗影响较大。但是当走线在顶层或底层时,差分阻抗就比较好控制,很容易达到设计要求,通过实际计算发现,重要的信号线最好走表层,容易进行阻抗控制,尤其是时钟信号差分对。

2、在PCB设计之前,首先必须通过阻抗计算,把PCB的叠层参数确定,如各层的铜厚,介质层的厚度等等,还有差分走线的宽度和间距都需要事先计算得出,这些就是PCB的前端仿真,保证重要的信号线的阻抗控制满足设计要求。

3、关于介电常数Er的问题:

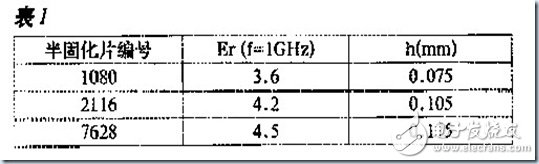

以我们使用最多的FR-4介质的材料板为例:实际多层板是芯板和压合树脂层堆叠而成,其芯板本身也是由半固化片组合而成。常用的三种半固化片技术指标如下表1 所示。