今天小编要和大家分享的是模拟技术相关信息,接下来我将从数字电路中二进制同步计数器实验原理及过程,惠美示波器这几个方面来介绍。

模拟技术相关技术文章数字电路中二进制同步计数器实验原理及过程

一。实验要求

1.1.实验目的

- 认识二进制同步计数器的定义、工作状态及信号波形;

- 熟悉基于JK触发器实现二进制同步计数器的构成规则。

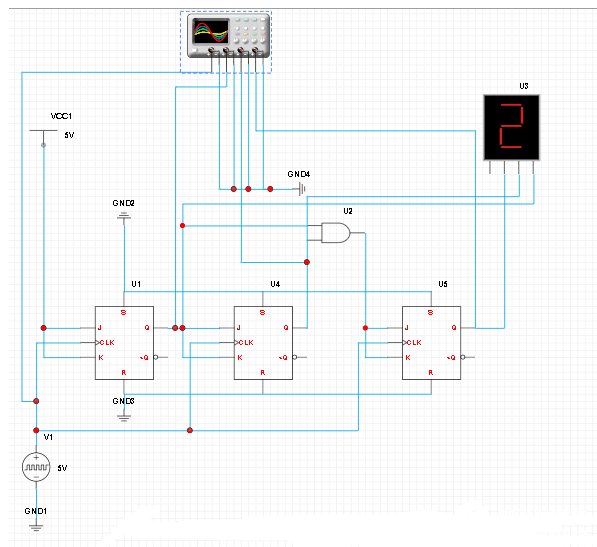

1.2.实验器材

- VCC

- Ground

- 脉冲电压源

- 上升沿触发JK触发器

- 2输入与门

- 四输入七段数码管

- 四通道示波器

1.3.实验原理

计数模值M和触发器级数k的关系:M=2k。

加法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0•Q1•…。 •Qi-1 i=1、2…。。(k-1)

减法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0‘•Q1’•…。 •Qi-1‘ i=1、2…。。(k-1)

1.4.实验内容、要求及过程

实验要求:

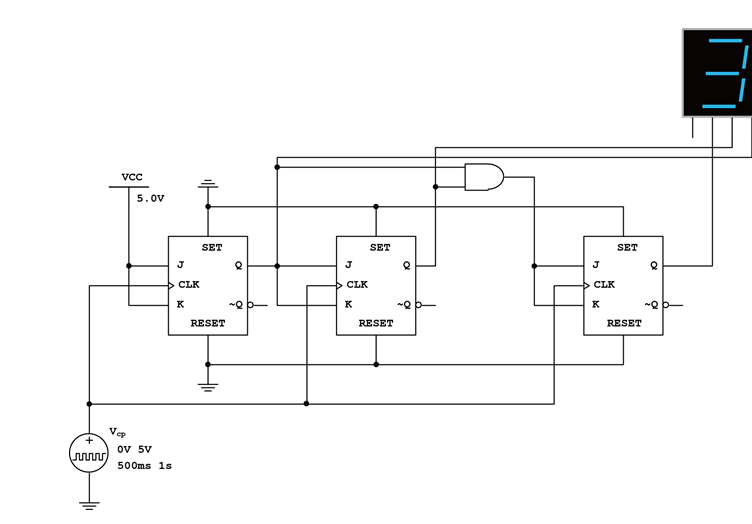

构建图1电路。时钟clk为0~5V,周期1s,高电平时长500ms。

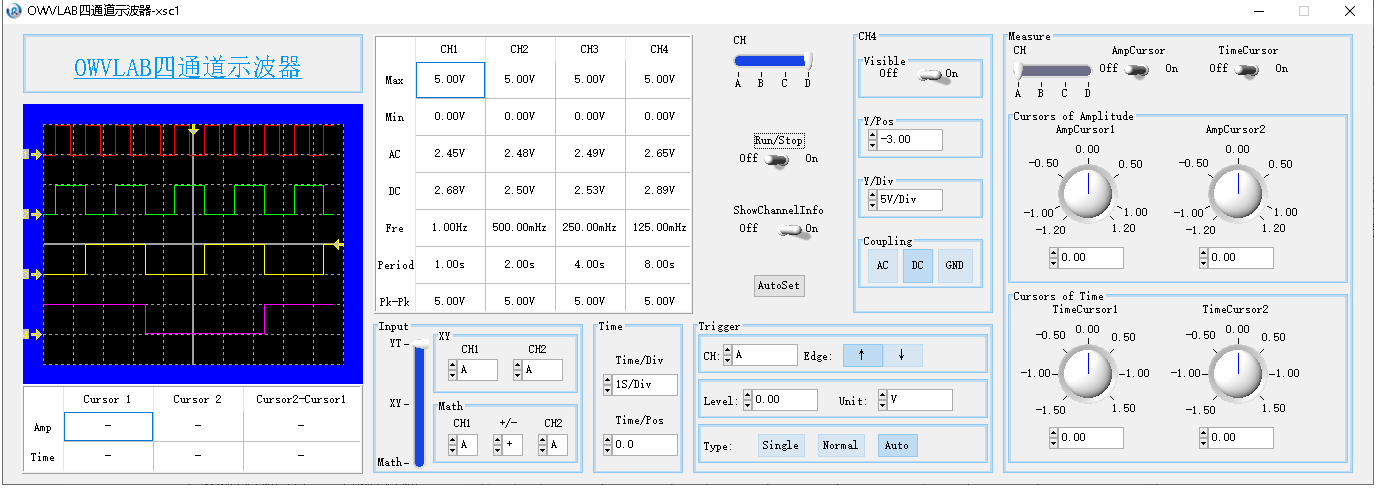

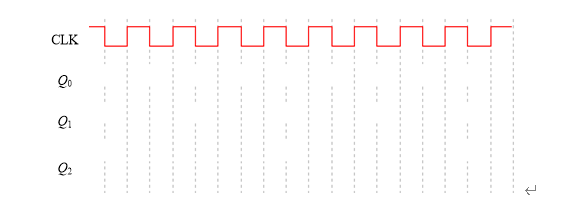

用四通道示波器观察时钟clk及各级触发器输出的Q0、Q1、Q2信号。根据观察,在图2中画出Q0、Q1、Q2的波形(与clk信号的边沿对应好,从Q2Q1Q0=000的状态开始),并观察数码管的显示情况。

二。实验图