校准电路设计

长期以来,由于CMOS工艺中存在匹配误差,完全依靠工艺本征匹配实现电流型CMOS DAC将很难超过10位精度,同时DAC的动态特性也会随着时钟频率和信号频率的增加而变差。

通过减小寄生电容、缩短建立时间仍是解决DAC电路中动态特性最直接有效的方法。但是为了保证DAC静态特性,减少梯度误差和随机失配就需要增大晶体管尺寸和复杂的布局,这样就会增大寄生电容和电阻,在提高静态特性的同时会限制DAC采样率和高频性能。

为了能够较好解决上述问题,我们可以采用校准技术,既能在保证电路高精度的同时减小电流源矩阵在DAC中所占的面积,又缓解了电路对版图和工艺的严格要求。因此,校准技术在保证DAC静态特性的同时能有效提高动态特性,同时还能降低电路对工艺、温度的敏感性,保证DAC长期稳定地工作。

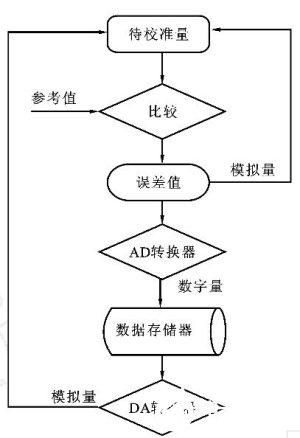

图2 自校准流程图

本论文采用了一种新的适合高精度、高速度DAC电路的自校准技术。这种自校准技术能够有效地校正各个电流源的失配,并降低对电流源输出电阻的要求。图2所示为我们采用的数字自校准方案的流程图。从该流程图中可见,在这个自校准的过程中,我们首先将待校准量与参考值进行比较,比较后的结果经一个ADC转换后存储到静态数据存储器(RAM)中,由此形成一个唯一对应的数字校准信号再送到一个校准的DAC中,最后完成待校准量的自校准。

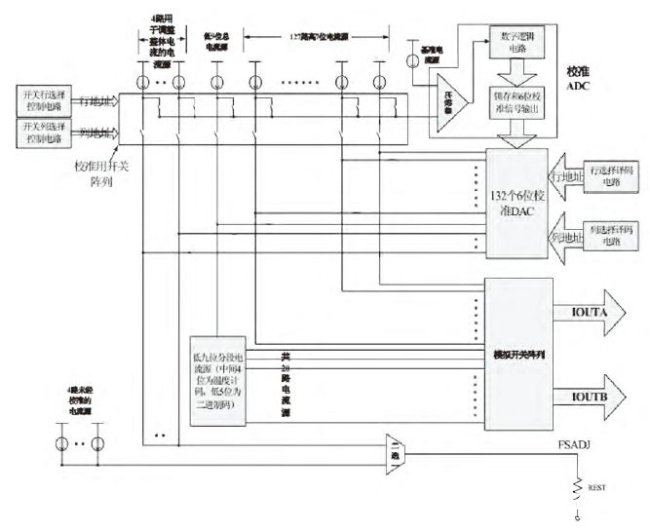

图3 自校准电路原理图

图3所示为实现上述自校准过程的电路原理图,为了保证整个DAC电路具有16位的线性度,芯片设计中内置了132个用来校准电流源输出线性度的DAC,它们分别是图中的127路高7位电流源,1路低9位的总电流源和4路用于调整输出增益的电流源,另外还有一路基准电流源。当进行自校准时,开关的行列选择电路将每一路电流源按顺序选通到比较器的输入端和基准电流源进行比较,比较后的结果经数字逻辑处理后将6位数字信号输入到相应的校准DAC的6个输入端。每路电流源都有一个校准DAC与其唯一对应,当选择相应电流源时也就对应选上了相应的校准DAC,选择DAC也需要相应的行列选择电路进行按顺序的选定。当一路电流源完成校准后,其唯一对应的校准DAC的6位数字值也已经确定并存在了静态存储器中,也就是所需调整的电流量已经加在了相应的电流源上。高7位中的每路电流源都有一个校准DAC来进行输出电流调整,低9位则是进行整体的电流调整,高7位和低9位电流源输出的电流经校准DAC校准后通过模拟开关阵列最终输出到差分电流输出端。另外还有4路电流源是用于设定整个电路输出电流范围的,这4路电流源经相应的4个增益校准DAC校准后,其总输出电流流过电阻RESET后可调整整个DAC的输出电流增益。