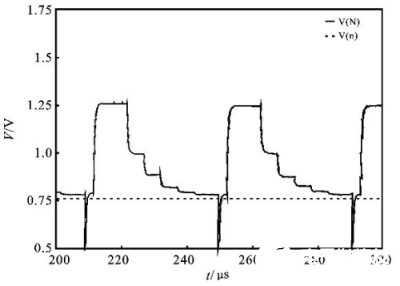

图4 自校准过程仿真波形图

图4给出了上述自校准过程的仿真波形,从图中的仿真结果我们可以看到,待校准电流源的输出在不断趋近基准电流源的输出,并且这个过程在不断地重复,直至所有的电流源均校准完毕为止。所有校准完毕的电流源最后经电流源开关阵列输出到差分电流输出端,这样就完成了整个电流源的校准过程。通过上述自校准过程,既保证了整个电路输出的线性度,同时也调整了电路输出的增益误差,优化了输出特性。

整体测试结果和电路概貌

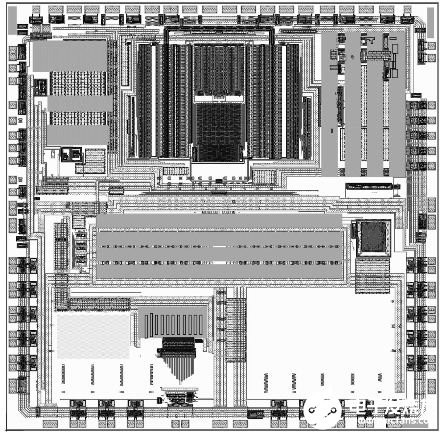

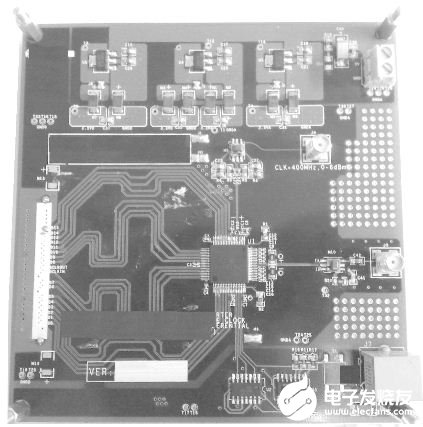

基于0.25微米混合信号CMOS工艺技术,并采用上述自校准电路设计方案,我们完成了一个采用分段式电流舵结构的16位400MSPS的D/A转换器芯片的版图设计,如图5所示,该电路芯片尺寸为4.9×4.9mm2,整个DAC电路一共有110个压焊块。目前该电路已经成功完成工艺流片,电路测试评估板的实物照片如图6所示。

图5 DAC芯片的版图示意图

图6 电路测试评估板

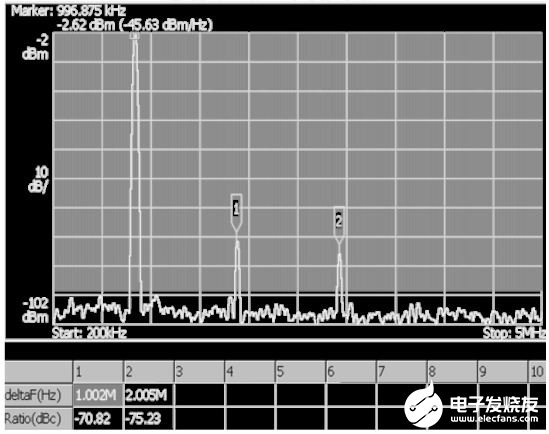

图7 系统的SFDR结果图(不带校准)

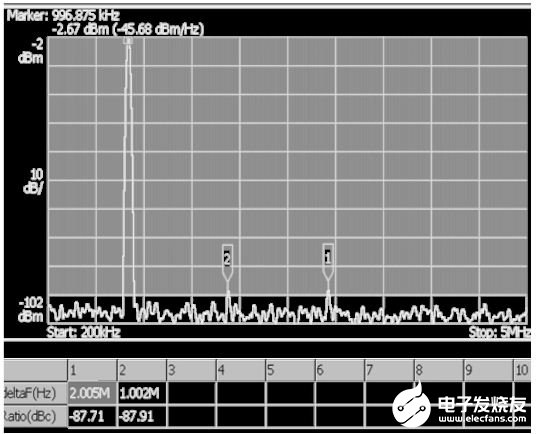

图8 系统的SFDR结果图(带校准)

对封装后的DAC电路进行的初步测试结果表明,该DAC电路工作正常。图7为系统不带校准的实测SFDR,图8为系统带校准后的实测SFDR。可见经过自校准后,电路的SFDR提升了十几个dB,并且谐波也明显减小。

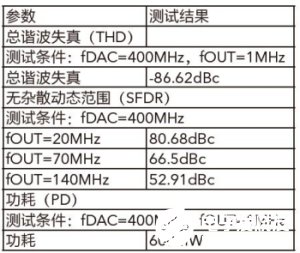

表1 400MHz时钟下,自校准后的转换测试结果统计表

我们对该DAC芯片还进行了其它各项指标的测试,电路在400MHz时钟频率下经过自校准后的测试结果如下表1所示。由表中各项测试数据可见,该芯片的各项性能参数指标优异,表明整个DAC芯片的性能良好。

总结

基于0.25微米Mixed-Signal CMOS制造工艺,本文设计并实现了一个高速高精度单片集成化的数模转换器(DAC)。论文中的DAC电路采用分段式电流舵结构,其时钟的采样频率为400MHz,分辨率为16Bit。电路设计中还采用了电流校准技术,既保证了DAC电路的高精度,也减小了梯度误差的影响。实际流片后的测试结果表明,自校准技术的采用可使DAC