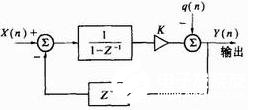

图1Σ-Δ调制器基本结构

习惯上,定义调制器中含有的积分器个数为调制器的阶数L,量化器的个数为级数。对调制器的线性模型做离散域的z变换分析,并将量化误差模型化为噪声信号,可以推导出输出信号Y对输入信号X与量化误差E的传递函数,在有效信号频率内,输入信号保持不变而噪声信号被差分衰减,即

Y(z)=z-LX(z)+(1-z-1)LE(z) (1)

通常,对调制器性能评测的重要参数之一是信噪比SNR,即信号功率与噪声功率之比

(2)

(2)

这里ps为有效信号的功率,对正弦信号来说,ps=

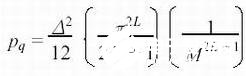

,A为幅度;pq是信号频带内总的量化噪声功率,由E(z)的传递函数在有效信号频带内积分得到

(3)

从上式可以看出,分别提高M或L都能带来SNR的提高。但当信号频率达到几十MHz以上的高频范围后,M的提高势必会受到现有工艺,以及功耗等制约。目前,更多的研究改善SNR的方法是针对L的提高。

从调制器内在稳定性考虑,针对高阶调制器(L≥3),又有两种结构上的取向,即单级single-loop结构和多级级联的MASH结构。

2.2过采样及MASH(多级噪声成形)技术

本文中使用记号fN来表示Nyquist调制器工作时的采样率,而它与基带信号最高频率fB的关系工程上一般为fN≈2.2fB~2.5fB。所谓过采样,就是指采样速度fs远大于fN。这里称M=fs/fN为“过采样比”。在Σ-ΔADC的设计中,M远大于1,且取为2的整数次幂(如32、64等)。过采样带来的好处为压缩基带内量化噪声,降低对输入端模拟滤波器的要求等。

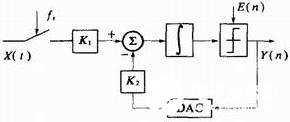

但是,光凭过采样来压缩基带内噪声是低效率的,提高4倍采样率才相当于提高1bit分辨率。为了更有效地衰减基带内量化噪声,应在过采样条件下进一步加入噪声成形(noise shaping)技术。最基本的一阶噪声成形器即所谓的一阶Σ-Δ调制器,其原理此处不再讨论。这里只指出,它可被转化为如图2所示的离散时间等效模型。