由于线性运算,校准ADC(DS2)自身必须要有高的线性。这需要在DS2中使用1位内部量化器。但是,由于DAC非线性信息保持,线性影响(增益和偏移误差)在DS2中是可以接受的。同样,实际DAC误差传输函数(从v1至d1)和其数字复制部分NLF(z)之间的匹配误差对整个转换器的线性仅有较小的影响。

3.3仿真结果

数字校正ADC(如图4的DS2)的运行仿真条件如下述。假设5bit(322电平)内部ADC和DAC,在DAC中有0.1%线性梯度误差。这符合中等误差0.4%的要求。在所有电路中,所有运放和任意失配电容(有0.1%标准偏差)的有限直流增益设定为54dB。使用OSR=4。在DS1中加入峰值为0.45V的中频双音调输入信号u1,采用二阶单位Σ-ΔADC实现DS2。为了论证利用校准可得到的高线性,DS1被接入在220MASH(包含10bitADC作为其第二级)中。这里不考虑在MASH(多级噪声整形)各级中的失配,它同样可由数字方法校正。

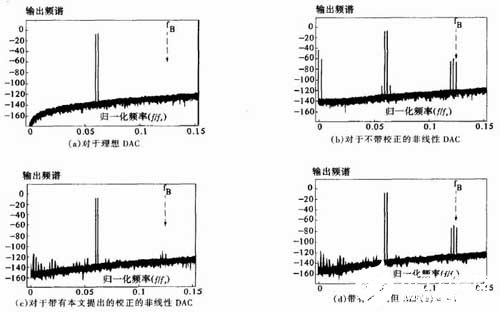

采用理想DAC、非理想运放和电容,系统运行计算出的频谱如图5(a)所示。图5(b)给出了使用误差校准的非线性DAC得到的频谱。可以看出,产生了大的谐波,SFDR仅为52dB。当使用了本文提出的数字校正技术后,频谱结果如图5(c)所示,得到SFDR>100dB。为了得到这样高的SFDR所需要的充分精确的eD估计,DS2对DAC的每一电平进行了218采样(如果DS2时钟控制在fs=5MHz,那么后台校准完整循环需要约4秒)。最后,图5(d)说明了使用NLF(z)=-1后的有害影响,即SFDR由101dB降至60dB。

图5MASH的输出频谱(215采样,64倍FFT,fB=fs/8,OSR=4)

5结论

本文介绍了Σ-Δ调制器的基本原理和技术,并针对采用多位内部量化器的MASH Σ-ΔADC提出了一种即时数字校正方法。对于低过采样比的模数转换器,采用通常的失配整形技术效果不佳,但本方法可有效应用于此。通过仿真证明,使用本文提出的即时数字校正法可得到极好的线性。

责任编辑:gt

关于模拟技术就介绍完了,您有什么想法可以联系小编。