3.1校正系统

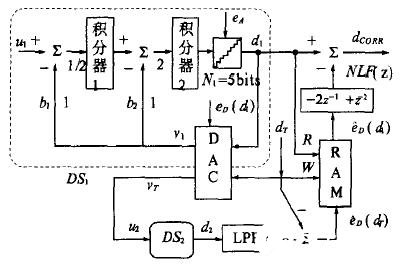

以二阶Σ-Δ调制器(DS1)为例来说明给出的校正技术。如图4所示,内部DAC有两个输出:v1和vT,分别输入到循环滤波和校准ADC(DS2)。由校准ADC得到^eD,即所有输出电平的DAC误差eD的数字估计,并且其被存储在RAM中。在转换时,通过FIR滤波器NLF(z)过滤RAM的输出,从而校正内部DAC误差,并从DS1的数字输出d1中减去过滤输出结果。获得^eD的过程和系统的详细分析在以下内容中给出。

图4带有误差校正的Σ-Δ调制器

在图4所示系统中,假设单独DAC输出为两个积分器提供反馈信号。系数b1、b2的不匹配对系统线性没有影响。值得注意的是,系统没有对内部ADC的非线性误差进行校正。这些误差被与量化噪声同样的噪声传输函数所抑制,其很少作为问题提出。当使用很低的OSR时,这样是不够的,就高线性而言,需要增加阶数或使用ADC元件失配整形。

3.2校正方法

实际DAC输出电平误差的即时获得适应于DAC的结构。如果DAC可提供多重输入和输出,那么离线校准能够被传输到后台进程。如果那样,对于DAC的每个可能的输入,数字校准信号dT将提供阶梯波形。通过校准Σ-Δ转换器DS2,每个DAC输出电平vT被转换成数字形式d2,然后通过LPF低通滤波而消除DS2的量化误差。然后,减去dT从而补偿电平误差eD,这样,得到误差估计^eD并将其存储在RAM中,并且对每一输出d1将再次调用^eD并校正。在运行过程中,周期性地重复校准,以追踪DAC输出电平中产生的漂移。

在低过采样率(OSR)和低阶循环滤波器情况下,从DAC的输出v1到DS1的输出d1的传输函数不能由NLF(z)=-1正确地近似。为了得到精确的误差校准,如图4所示,RAM的输出需要被实际的NLF(z)(此处为-2z-1+z-2)过滤。

在一些DAC的实现中,使用了N个等价单位元件(电流源、电容、电阻等)。如果在DAC中执行N+1个元件,可使用上述算法,利用DS2逐个顺序地测量它们的误差。换句话说,输出信号d1与校准信号dT一样可被使用。利用n个单位元件通过调用d1值从而产生v1,剩余的N-n个单位元件被用来产生vT。如果DAC增益和偏移误差是可以被接受的,为了使所有单位元件误差总和可取零,那么vT中的误差是v1中误差的负数。因此,通过将vT中的模拟采样分类进入通道,使用其中一个通道专用于每个可能输入(d1)码和其补码,DS2可用来以数字形式产生单独DAC电平。由于为每一DAC电平复制存储元件(反馈电容),DS2的运算可容易地在通道中多重复用。