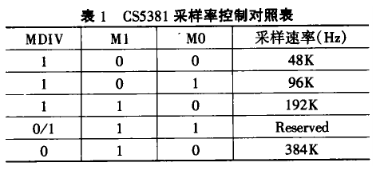

通常24位ADC都会产生一个微小的直流偏移,在CS5381内部有一个数字高通滤波器,可以通过给管脚HPF提供一个低电平使该滤波器有效,这样,芯片可以消除直流偏移。另外芯片还带有溢流监测器,当模拟信号的输入电压幅度过大而致使ADC转换溢出时,相对应的管脚LFV变低,因此,在该管脚与电源之间接一个发光二极管,就可以直观地显示出模拟输入是否溢出,从而根据需要调整前端放大电路的增益。

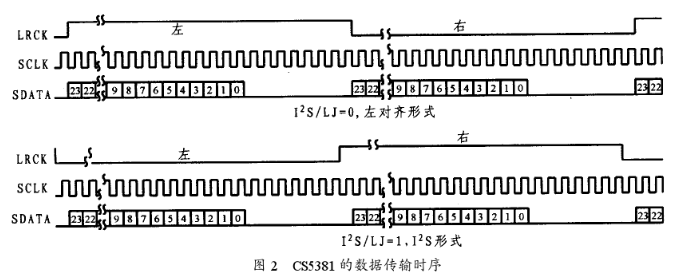

CS5381的模拟信号为差动输入方式,因此,它的前端要有一个简单的模拟调理电路。CS5381的转换结果是24位补码形式的串行数据,且左右通道交替输出,可用LRCK的高低电平来进行区分。输出数据有两种格式:左对齐和I2S。图2是CS5381的两种数据传输时序。

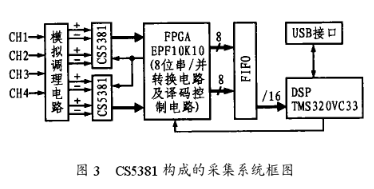

3、四通道并行采集系统的设计

图3所示是一个四通道并行采集系统的整体框图,该系统主要由TMS320VC33(以下简称VC33)、两片CS5381、一片FPGA(EPF10K10)和一个大容量FI-FO存储器构成。采集系统与主机的通讯采用USB接口。系统中的一片CS5381工作于主模式,另外一片则工作在从模式下,这样可以保证两片ADC工作时严格同步。

在基于CS5381的采集系统中,如何实现CS5381与TMS320VC33的接口是一个关键问题。具体的设计方案有两种:其一,由于CS5381采用同步串行数据输出方式,而TMS320VC33具有多通道缓冲串口(McBSP),因此,可以较为容易地实现二者的硬件连接。其二是通过CPLD/FPGA设计串并转换电路,并把CS5381输出的串行数据转换为并行数据,然后由TMS320VC33通过扩展IO对数据进行读取。这两种方案相比,第一种方案比较简单,但系统要设计四个独立的同步采集通道,并要使用两片CS5381,而TMS320VC33只有一个McBSP,所以此方案无法采用。第二种方案实现起来相对比较麻烦,硬件成本也较大。它通过把每片CS5381的串行数据转换成8位并行数据并经FIFO缓存,然后由TMS320VC33通过中断和DMA方式对四个通道的转换数据进行读取。