串并转换电路设计是CS5381和TMS320VC33接口电路的核心部分,它负责将CS5381输出的串行数据转换为并行数据并存储在FIFO中,同时产生相应的FIFO写信号。具体设计时,应当考虑以下三个问题:

(1) 对于CS5381在左右通道的数据,除了24位转换结果数据外,还应输出一个8位的附加信息,因此,输出一道数据时,总共有32个时钟输出,而最后8位数据是无用的,这样,就需要有一个禁止逻辑来防止8位附加数据也写入到FIFO中。

(2) 由于串行输出时钟SCLK在CS5381工作期间是一直存在的,因此,在启动和结束串并转换时,应该有一个控制逻辑来使串并转换电路只有在LR-CK的上升沿(或者下降沿)触发下才能进行数据转换,以保证左右通道数据顺序的确定性。

(3) 转换电路要有使能控制,以便控制信号的采集时间。

4、测试结果

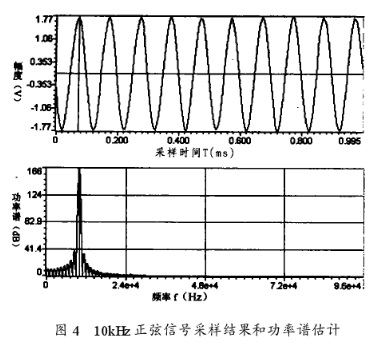

该采集系统利用标准信号源进行正弦信号采集测试,下面是对两种频率的正弦信号进行测试的结果分析。其中第一种测试结果如图4所示。对于10kHz的正弦信号,CS5381的主时钟MCLK为24.576MHz、它具有64倍的过采样率(采样速率fs=MCLK/64=192kHz),采样时间T为1ms。由采样结果和功率谱可以看出:系统中的CS5381采样数据在频率域的动态范围在120dB以上。

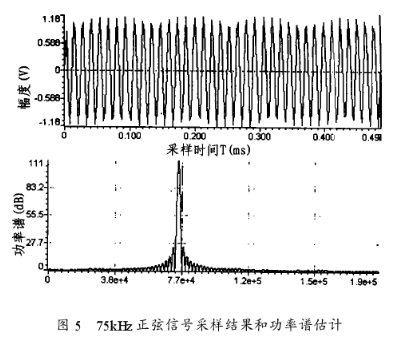

把系统采样速率fs设置为384kHz时,对75kHz正弦信号的采样结果及功率谱估计如图5所示,由采样结果可以看出:CS5381可以在384kHz的采样速率下对更高频率的信号进行采样,但从功率谱可以看出,此时动态范围及信噪比都在80dB左右,可见采样精度有较大幅度的降低。若要完成更高频率信号的采样,在对采样精度要求不是特别高时,可以考虑采用这种方式。

由此可以看出,由CS5381构成的这种采集系统具有分辨率高、动态范围大等特点,在混场源电磁法接收机中得到了很好的应用,可以对带宽为DC~75kHz、动态范围为120dB的电磁信号进行高精度数据采集。

责任编辑:gt

关于模拟技术就介绍完了,您有什么想法可以联系小编。