今天小编要和大家分享的是模拟技术相关信息,接下来我将从高速数据速率系统的信号完整性解读,面向usb3.0的高效静电防护解决方案兼具完美的信号完整性这几个方面来介绍。

模拟技术相关技术文章高速数据速率系统的信号完整性解读

信号完整性是许多设计人员在高速数字电路设计中涉及的主要主题之一。信号完整性涉及数字信号波形的质量下降和时序误差,因为信号从发射器传输到接收器会通过封装结构、PCB走线、通孔、柔性电缆和连接器等互连路径。

当今的高速总线设计如LpDDR4x、USB 3.2 Gen1 / 2(5Gbps / 10Gbps)、USB3.2x2(2x10Gbps)、PCIe和即将到来的USB4.0(2x20Gbps)在高频数据从发送器流向接收器时会发生信号衰减。本文将概述高速数据速率系统的信号完整性基础知识和集肤效应、阻抗匹配、特性阻抗、反射等关键问题。

随着硅节点采用10nm、7nm甚至5nm工艺,这可以在给定的芯片尺寸下实现高集成度并增加功能。在移动应用中,趋势是更高的频率和更高的数据速率,并降低工作核心电压如0.9v、0.8V、0.56V甚至更低以优化功耗。

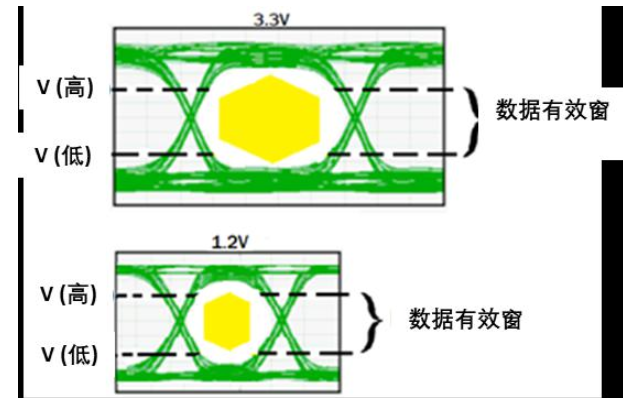

在较低的工作电压下以较高的频率工作会使阈值电平或给定位数据的数据有效窗口变小,从而影响走线和电源层分配功率以及“眼图”的闭合度。

由较高频率和较低工作电压引起的闭眼,增加了数据传输误差的机会,因而增加了误码率,这就需要重新传输数据流。重传会导致处理器在较长时间处于有源模式以重传数据流,这会导致移动应用更高的功耗并减少使用日(DOU)。

图1. 频率和较低电压对眼图张开的影响

在给定的高频设计中增加其它设计挑战如信号衰减、反射、阻抗匹配、抖动等时,很明显,信号损耗使接收器难以正确译出信息,从而增加了误差的机会。

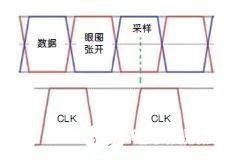

数据流中的时钟采样

在接收器处,数据是在参考时钟的边缘处采样的。眼图张开越大,就越容易将采样CLK设置在给定位的中间以采样数据。任何幅值衰减、反射或任何抖动,都将使眼图更闭合并使数据有效窗口和有效位时间变得更窄,从而导致接收端出现误差。