图2. CLK采样

现在,让我们检查何时需要将通道或互连视为传输线,并查看在智能手机或平板电脑等系统中传输损耗的一些主要原因。

高频和传输线

低频设计是指波长远大于线长度且PCB走线和互连的电阻与频率无关,因此传输线的影响可以忽略不计。高频设计是指波长远小于线长度且走线的所有物理特性和互连尺寸都需要控制,以便具有一系列电气特性的传输线可用于给定应用。

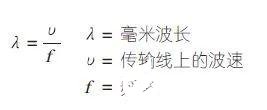

我们将互连视为传输线的时候是在最高频率下工作时,走线长度可能超过该频率波长的1/10。此时,我们需要使用集总元件对走线建模,并考虑所有频率相关元件,包括寄生电容和电感及其对信号衰减的影响。

另一种确定在什么频率下将互连线视为传输线的方法是考虑信号的上升时间(tr)。

在大多数纳米工艺节点中,高数据速率信号具有急剧的上升/下降时间,这要求将通道或任何互连视为传输线。当这些信号通过信道传播时,其带宽和传输受给定的信号上升时间控制。

传输速度

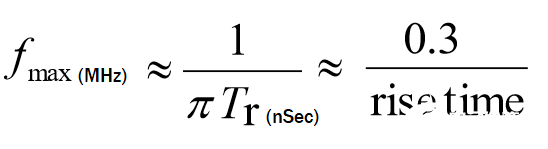

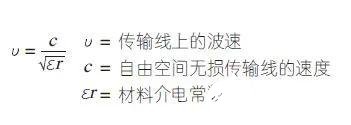

电信号是电磁波,其传输速度取决于其周围材料的介电常数。传输速度的公式是

图3. 传输线上的波速

自由空间(介电常数为1)无损传输的波速约为3 x 108 m / s,不同于介电常数为4的传输线的波速,后者导致波速降低一半或1.5 x 108m / s。在自由空间对比在PCB传输的波速差异将导致称为传播延迟(Td)的时间延迟,Td取决于传播的媒介和信号必须传播的距离。

Td(传播延迟)=传播距离/ Vp(传输速度)

现在,当一个信号(CLK)在外层传播而另一信号(Data)在内层传播时,若我们在一侧具有自由空间而在另一侧具有介电常数时,情况会怎样呢?

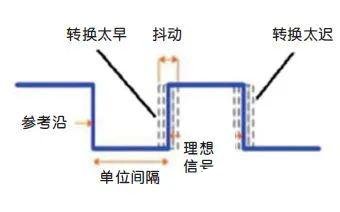

在许多设计中,高频信号必须以互连电缆或挠性电缆作为传输路径的一部分,这会对幅值和时序波形产生延迟和偏差。由于信号速度降低、串扰或介电材料吸收的任何能量而导致的时序偏差或任何其它损耗都会同时产生称为抖动的时序和幅值偏差。

图4. 抖动

在这里,设计人员必须匹配一系列信号之间的飞行时间。由于内层的DATA信号将传播得较慢,因此我们必须减小DATA信号的长度以匹配CLK信号的飞行时间。

集肤效应

如果我们查看称为C1的给定导体的 一部分并通过它发送电流I(t),根据安培定律,将会产生与通过导体的电流成比例的磁通量。如果我们仅考虑一个导体,附近没有其它导体,那么通量线(B1)将在导体C1中沿与磁场B1相反的方向产生循环涡流。