为了适应逐渐增加的异构计算场景,各个厂商开始筹划推出新的总线技术,这包括:

来自 Intel 的 Compute Express Link(CXL)

来自 IBM 的 Coherent Accelerator Interface(CAPI)

来自 Xilinx 的 Cache Coherence Interconnect for Accelerator(CCIX)

来自 AMD 的 Infinity Fabric

来自 NVIDIA 的 NVLink

毫无例外,不同厂家的技术都提供了对 Cache Coherence 的支持,这正是 PCIe 总线所缺乏的,也是工业界所需要的。目前这场关于下一代总线的竞争还在进行中,但大家认为能笑到最后的恐怕还是 Intel 所支持的 CXL。

这里我们只对 CXL 做一个简单的介绍。

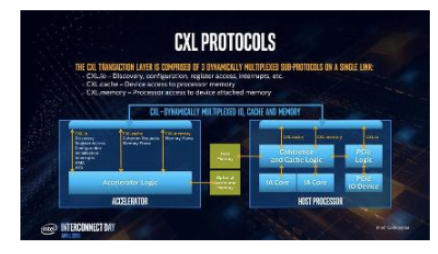

CXL 协议中定义了 3 种子协议:

http://CXL.io:不提供 Cache Coherence 的 IO 访问,类似于目前的 PCIe 协议

CXL.cache:用于设备访问主存

CXL.memory:用于 CPU 访问设备内存

例如对于一个 GPU 设备,可以通过 CXL 来进行 GPU 到 CPU,GPU 到 GPU 的数据交换。而由于 CXL 支持 Cache Coherence,这个过程将变得非常简单,这无疑是一个重大的变化。而对于存储设备来说,CXL 使得 PMem 无论是作为持久化内存还是易失性内存,都可以不仅仅局限在内存总线,而是可以通过 CXL.memory 和 CPU 进行通信。这意味着 PMem 未来不仅仅可以提供类似目前 NVMe 设备的热插拔功能,还可以摆脱内存总线对散热和功耗的限制。甚至更进一步,未来可能会出现 CXL over Fabric 的技术,CPU 可以通过 CXL 协议访问远端内存。

CXL 1.0 将采用和 PCIe Gen5 向兼容的硬件标准,这样一来硬件厂商不需要为适配不同协议而生产两种不同接口的硬件设备,统一采用 PCIe Gen5 的标准就可以了。如果在设备协商阶段发现对端支持 CXL 协议,那么就可以采用 CXL 协议运行,否则可以采用 PCIe Gen5 运行。

CXL.cache 和 CXL.memory 组成了一个异构的 Shared Memory 系统,这对传统的 Shared Memory 系统是一个极大的扩展,让异构计算变得更加简单。而 CXL over Fabric 可能会组成一个由硬件支持的 Distributed Shared Memory 系统,这将使 Memory-level Composable Infrastructure 成为可能。在未来的数据中心,很可能会出现专门用于池化内存的服务器,CPU、内存像乐高一样搭建起来将真正成为现实。而这一切都有可能在未来的 5~10 年内发生。