创建存储器控制器是一项极其复杂、精细的任务,FPGA 设计人员要解决面临的一道道难题,就需要 FPGA 随附的工具提供更新水平的集成支持。

为设计的完整性起见,对包括存储器控制器状态机在内的所有构建模块加以集成,十分必要。控制器状态机因存储器架构和系统参数的不同而异。状态机编码也可以很复杂,它是多个变量的函数,例如:

架构(DDR、DDR2、QDR II、RLDRAM 等)

组 (bank) 数(存储器器件之外或之内)

数据总线宽度

存储器器件的宽度和深度

组和行存取算法

最后,数据与 DQS 比 (DQ/DQS) 这类参数会进一步增加设计的复杂性。控制器状态机必须按正确顺序发出命令,同时还要考虑存储器器件的时序要求。

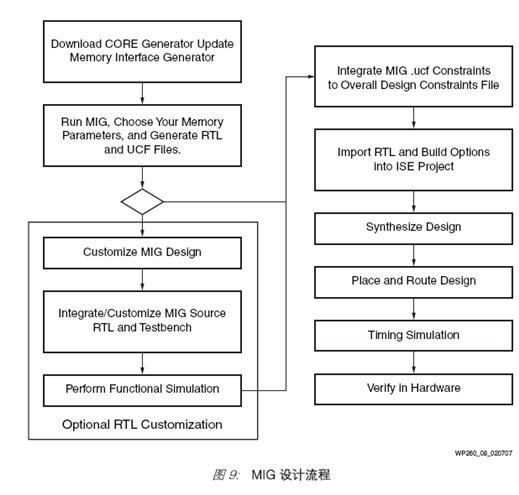

使用 MIG 软件工具可生成完整的设计。该工具作为 CORE Generator 参考设计和知识产权套件的一部分,可从 Xilinx 免费获取。MIG 设计流程(图9)与传统 FPGA 的设计流程非常相似。MIG 工具的优点是不必再为物理层接口或存储器控制器从头生成RTL 代码。

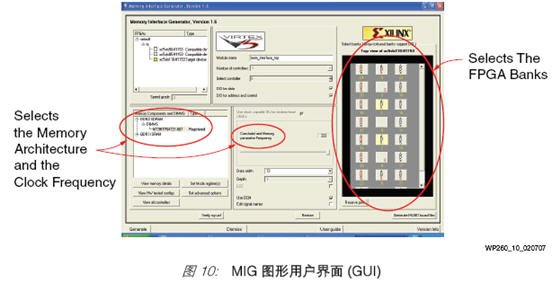

MIG 图形用户界面 (GUI) 可用于设置系统和存储器参数(图10)。例如,选定 FPGA器件、封装方式和速度级别之后,设计人员可选择存储器架构,并挑选实际存储器器件或 DIMM。同是这一个 GUI,还可用于选择总线宽度和时钟频率。同时,对于某些FPGA 器件,它还提供拥有多于一个控制器的选项,以适应多个存储器总线接口的要求。另外一些选项可提供对时钟控制方法、CAS 延迟、突发长度和引脚分配的控制。

用不了一分钟,MIG 工具即可生成 RTL 和 UCF 文件,前者是 HDL 代码文件,后者是约束文件。这些文件是用一个经过硬件验证的参考设计库生成的,并根据用户输入进行了修改。

设计人员享有完全的灵活性,可进一步修改 RTL 代码。与提供“黑匣子”实现方法的其他解决方案不同,此设计中的代码未加密,设计人员完全可以对设计进行任意修改和进一步定制。输出文件按模块分类,这些模块被应用于此设计的不同构建模块:用户界面、物理层、控制器状态机等等。因此,设计人员可选择对控制组存取算法的状态机进行自定义。由 MIG 工具生成的 Virtex-4 和 Virtex-5 DDR2 的组存取算法彼此不同。Virtex-5 设计采用一种最近最少使用 (LRU) 算法,使多达四组中的一行总是打开,以缩减因打开/ 关闭行而造成的开销。如果需要在一个新组中打开一行,控制器会关闭最近最少使用组中的行,并在新组中打开一行。而在 Virtex-4 控制器实现中,任何时候只有单个组有一个打开的行。每个应用都可能需要有自己的存取算法来最大化吞吐量,设计人员可通过改变 RTL 代码来修改算法,以更加适合其应用的访问模式。