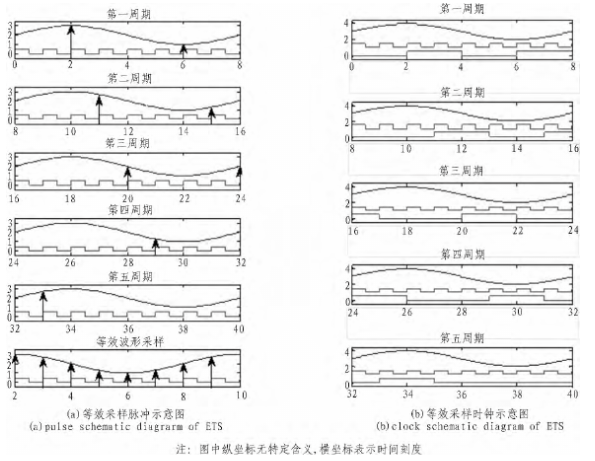

等效时间采样中每个周期可以采集多个点时的理论依据,给出了等效时间采样中每个周期可以采集单个点时的理论依据。

我们通过将高频时钟进行分频已达到或者接近满足处理速度时钟要求。在图1(b)中幅度最小的时钟信号为采样时钟。由图1(b)可以很清楚的看到分频后的时钟波形,分频后的时钟波形在时钟的上升沿对信号进行采样,那么就会得到如图1(a)中所表示的等效时间采样。

图1 等效时间采样示意图

2 、基于FPGA的等效时间采样实现

2.1 系统硬件实现框图

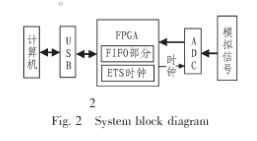

系统的总体框图如图2,FPGA 控制的等效采样时钟连接到ADC 器件的时钟部分,ADC 器件在时钟的控制下对宽带模拟信号进行采样,采集到的数据传送到FPGA 中的FIFO,FPGA 再将FPGA 中FIFO 的数据传递到USB 中的FIFO,然后USB 将USB 中FIFO 数据推送到计算机,计算机对接收到的数据进行重构处理。对于信号周期的获取,在电阻抗多频及参数成像技术中采集信号的周期是由发送信号的周期决定, 而对于其他复杂周期信号的周期获得可以通过所采用的方法获得。

图2 系统方案框图

2.2 等效时间采样时钟的程序实现

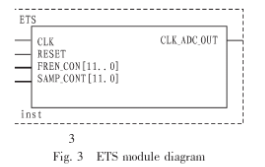

图3 展示了基于FPGA 生成的等效时间采样模块的输入端口与输出端口。其中CLK 表示高频时钟的输入,RESET表示的是复位输入端,FREN_CON 表示的是分频控制输入用于控制高频时钟的分频数,SANM_CONT 表示的是模拟信号的周期包含多少个高频时钟信号的波形,CLK_ADC_OUT 表示的是输出时钟端口,此端口连接到模数转换器件(ADC)的时钟输入端口。

图3 等效时间采样模块图

以下是实现等效时间采样所需时钟的代码:

SIGNAL SAMP_CONTS:STD_LOGIC_VECTOR (11

DOWNTO 0):=(OTHERS=》‘0’);

SIGNAL ADC_CLK_BANK:STD_LOGIC_VECTOR (11

DOWNTO 0):=(OTHERS=》‘0’);

SIGNAL CLK_CNT :INTEGER RANGE 0 TO 5000:=0;

SIGNAL CLK_TANK:STD_LOGIC:=‘0’;