SIGNAL EN :STD_LOGIC:=‘1’;

BEGIN

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN EN‘0’);

SAMP_CONTS‘0’);

EN

3、 波形仿真

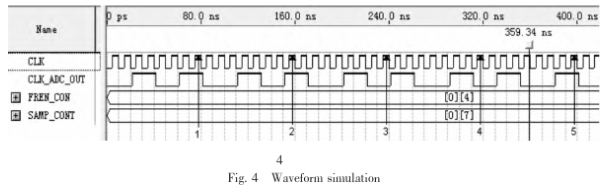

图4 中的波形仿真是以模拟信号的一周期等于8 个CLK 时钟周期,CLK_ADC_OUT 是对CLK 进行4 分频且分频后的时钟占空比为50%为假设的。1 号箭头指向的时钟上升沿标志着第一周期结束,上升沿之后进入第二周期。同理,2号箭头所指时钟的上升沿标志着第二周期的结束,上升沿之后标志着进入第三周期。

图4 波形仿真

在第一个周期中从CLK 的第一个上升沿开始计时同时对CLK 进行分频可以得到CLK_ADC_OUT 时钟信号, 在第一周期中在CLK 的第二个上升沿CLK_ADC_OUT 电平翻转(存在延时), 在第二周期中在第三个上升沿CLK_ADC_OUT电平翻转, 在第三个周期中在CLK 的第四个上升沿CLK_ADC_OUT 电平翻转。可以看出波形仿真图是对图1(a)、(b)两图表达时钟的实现。在这里应该注意到,在第一周期中虽然也有8 个CLK 的上升沿,但是并没有表示出如1 号箭头所指CLK 时钟上升沿之后与第二周期第一个CLK 时钟上升沿之间的波形。

4、 结论

本文介绍了等效时间采样的基本原理、系统实现的具体方案。等效时间采样技术实现了利用低速的ADC 器件对宽带模拟信号的采集, 降低了系统对ADC 器件的要求以及系统实现的复杂度。本文介绍的等效时间采样技术由于使用了FPGA 采样技术, 使得在被采样信号的一个周期中相较于一个周期仅能采集一个点的顺序等效时间采样有很大的提高,并且可以控制被采集信号一个周期中的采集点数从而可以根据后续器件处理速度实现变频控制采样。通过FPGA 实现等效采样时间,降低了系统实现的复杂度,同时可以十分方便的对代码进行修改使系统的调试更加简便。

责任编辑:gt

关于可编程逻辑就介绍完了,您有什么想法可以联系小编。