今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从基于FPGA器件和CPU控制实现数字锁相环频率合成系统的设计,fpga 转接板 空板 cpu dip 贴片转直插 128 lqfp144 tqfp eqfp qfp这几个方面来介绍。

可编程逻辑相关技术文章基于FPGA器件和CPU控制实现数字锁相环频率合成系统的设计

1 、引言

数字锁相环频率合成器已经广泛的运用在军事和民用无线通信领域,而用CPU控制的可编程大规模数字锁相环频率合成器则是其中的关键技术。当前,可编程逻辑电路在数字系统设计中飞速发展,很多中规模,甚至大规模的数字系统已经可以通过可编程逻辑电路来实现单片集成,即用一个芯片完成整个数字系统的设计。因此将CPU控制的数字锁相环频率合成系统集成在一块可编程逻辑芯片中实现已经成为可能。本系统由多个可编程的数字分频器、数字鉴频-鉴相器以及协调控制工作的CPU组成。

2 、系统结构

数字锁相环频率合成系统的工作原理是:锁相环对高稳定度的基准频率(通常由晶体振荡器直接或经分频后提供)进行精确锁定,环内串接可编程的分频器,通过编程改变分频器的分频比,使环路总的分频比为N(可通过编程改变),从而环路稳定的输出 N倍的基准频率,而整个程序和系统的控制是要由CPU来完成的。

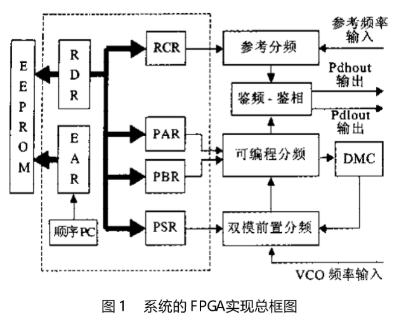

图1为CPU控制的数字锁相环频率合成系统的 FPGA实现方案。

图1中虚线部分为CPU模块,CPU通过读取 ROM和对相应的寄存器置数来完成系统的控制;EEPROM为外接ROM,保存系统设置和预置频点的数据;参考分频模块对输入的参考频率进行预分频,形成鉴频和鉴相的基准频率;鉴频-鉴相模块完成环路的鉴频和鉴相功能;可编程分频模块和双模前置分频模块共同组成环路内串接的可改变分频比的分频器;Pdhout和Pdlout是鉴频和鉴相输出的误差信号。误差信号再通过环路滤波器产生误差电压控制VCO,VCO的输出反馈至系统,经过分频和锁相过程,直到环路达到锁定状态,此时 VCO的输出即为所要求的稳定频率。

3、 参考分频模块

参考分频模块主要完成对参考频率(通常由外接晶体振荡器输入)进行预分频,从而输出鉴频和鉴相的基准频率。