CPU内的控制包括:读外部程序存储器(EEPROM)控制、程序执行控制、可编程分频器置数控制等。其工作过程如下:CPU的程序计数器采用顺序递增记数方式,从000H地址开始顺序执行,外部ROM中的指令也从000H地址顺序存放,而指令也不需要译码,是按照指令与存储地址相对应的方式:地址000H,执行RCR=(000H)h,PSR=(000H)l;地址001H到400H,存放预设的频点值表,执行PAR=(abcH)h,PBR=(abcH)l,其中(xxxH)h和(xxxH)l分别表示xxxH中存储数据的高4位和低4位,abcH表示当前执行的001H到3FFH中的某个地址。程序顺序执行到3FFH后,自动返回到001H地址循环执行。如果没有1023个频点,在最后一个频点以后的地址全存入FFH即可,当程序运行到内容为FFH的地址时就不进行任何操作而立即返回到001H地址继续循环执行。

读外部程序存储器控制部分采用一个10位的加法计数器,形成顺序递增的10位地址。同时还应有读使能read,并即时处理程序运行控制信号即锁定信号stop,当stop信号有效(低电平)时,频率合成器的输出锁定在当前的频点。模块还包括 10根地址总线,8根数据总线。程序执行控制部分通过当前地址给相应的寄存器赋值,产生不同的分频值。

仿真时采用Verilog HDL编写了一个预存数据的外部ROM仿真模块,用来对CPU进行仿真,程序如下:

module rom(_read,address,data);

input _read;

input [9:0] address;

output [7:0] data;

reg [7:0] data;

always @ (_read or address)

if(_read)

data《=8‘bzzzzzzzz;

else

case(address)

10’h000:data《=8‘ha8;

10’h001:data《=8‘h91;

…………………

10’h3fe:data《=8‘h87;

10’h3ff:data《=8‘h65;

endcase

endmodule

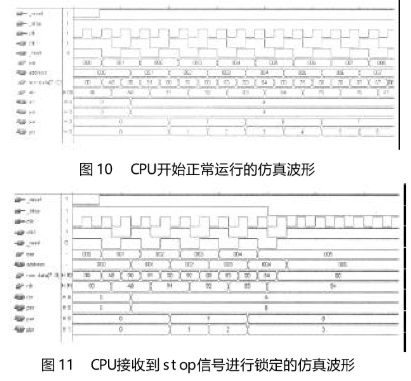

图10、11是其仿真波形。图中reset为复位信号;stop为锁定信号;clk为CPU的外部时钟;clk1是clk的2分频信号为CPU读取数据,产生地址等提供时钟;read也是clk的2分频信号(相位和clk1相差π/2),为外部ROM提供读使能,同时为CPU提供寄存器控制的时钟;address为外部ROM地址总线;rom.data[7..0]为外部ROM送出的数据。

责任编辑:gt

关于可编程逻辑就介绍完了,您有什么想法可以联系小编。