N=(M+1)×B+ M×(A-B)=MA+B ,即环路进行了N分频。

由以上分析可以看出来,PAR中的值必须要大于PBR中的值,否则模块将运行不正常。

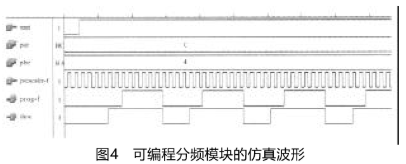

图4是可编程分频模块的仿真波形。图中re set 为复位信号;prescaler_f为双模前置分频后输出的频率;prog_f为经过两个可编程分频器分频后模块输出的频率;PAR预置的值为HC,即A=12分频;PBR预置的值为H4,即 B=4分频;dmc为双模控制逻辑。

6、 鉴频-鉴相模块

鉴频-鉴相模块主要完成对经过分频后输入模块的频率和基准频率进行鉴频-鉴相,并且输出误差结果。

此模块采用超前与滞后双输出方式:如果输入频率高于基准频率或相位超前,则Pdhout输出负脉冲,而Pdlout输出高电平;如果输入频率低于基准频率或相位滞后,则Pdhout输出高电平,而Pdlout输出负脉冲;当输入频率和基准频率同相后,Pdlout和Pdhout都输出高电平。

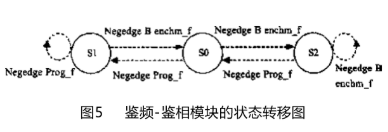

鉴频-鉴相模块的工作原理为:当输入频率和基准频率不同频时,模块工作在鉴频方式;当输入频率和基准频率同频但不同相时,模块工作在鉴相方式,从而扩展环路的快捕带,使环路较快的进行相位锁定,进而达到闭环锁定状态。数字鉴频—鉴相模块采用自底向上的设计方法,其输出方式与功能符合图5所示的状态转移图。

图中Negedge Benchm_f为基准频率波形的下降沿;Negedge Prog_f为输入频率波形的下降沿;S0状态,模块输出Pdhout=1,Pdlout=1,此时处于同频同相;S1状态,模块输出Pdhout=0,Pdlout=1,此时输入频率高于基准频率或者输入频率比基准频率相位超前;S2状态,模块输出Pdhout=1,Pdlout=0,此时输入频率低于基准频率或者输入频率比基准频率相位滞后。

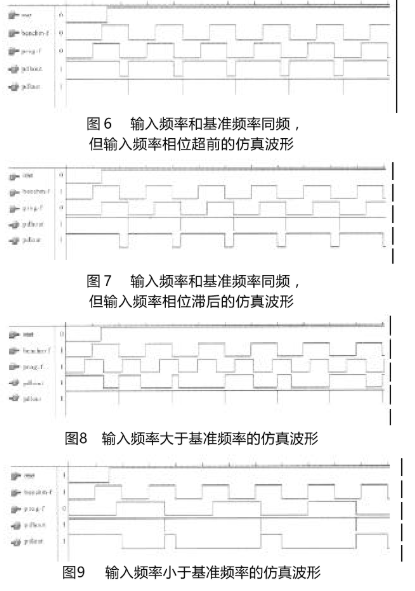

图6、7、8、9是不同输入频率时的仿真图。

图中reset为复位信号;benchm_f为基准频率;prog_f为输入频率;pdhout和pdlout为鉴频-鉴相模块的输出。

7 、CPU模块

CPU模块主要完成对整个系统的控制。CPU包括一个8位的读数据寄存器(RDR);一个10位的外部EEPROM地址寄存器(EAR),寻址空间为1024×8bit,支持1023个频点的频率合成;4个4位的分频寄存器,包括参考分频寄存器(RCR),前置分频寄存器(PSR),可编程分频寄存器A(PAR)和可编程分频寄存器B (PBR)。