CLK:系统时钟;

RES:异步全局复位信号,低有效;

SDATA:串行输入数据;

PDATA:并行输入数据;

SEL:设置输入数据为并行还是串行;

READ:读信号,低有效;

WRITE:写信号,低有效;

SRES:同步复位信号,高有效;

CLKI:外部CPU时钟;

A[3:0]:外部CPU访问内部寄存器的地址总线;

OUT:输出数据。

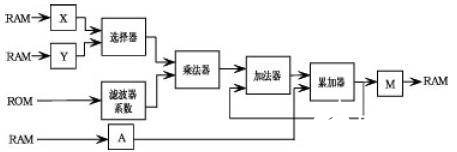

内部算术与逻辑单元是整个滤波器的核心,它的结构如图4所示。

计算过程是,X、Y为输入数据,通过选择器进入乘法器,算术与逻辑单元从系数ROM中读取滤波器的系数用以输入数据相乘,相乘的结果与前一步的结果相加进入累加器,累加器读取上一步计算的中间结果A并计算,最后将此步计算的结果M存入到RAM中去。

结语

本文介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的方法。在实际使用中,可以根据不同精度要求,方便地对该IIR滤波器进行修改以满足不同的指标要求,灵活地组成任意阶不同类型的滤波器。同时,在系统运行中,外部CPU可以灵活修改滤波器系数,改变滤波器的频率响应,满足特定的应用要求。

责任编辑:gt

关于FPGA,ASIC技术就介绍完了,您有什么想法可以联系小编。