今天小编要和大家分享的是FPGA,ASIC技术相关信息,接下来我将从采用可编程器件和多相滤波实现数字正交混频的设计方案,gpu,fpga芯片成为增强机器学习能力的\这几个方面来介绍。

FPGA,ASIC技术相关技术文章采用可编程器件和多相滤波实现数字正交混频的设计方案

引 言

传统的正交下变频是通过对模拟I、Q输出直接采样数字化来实现的,由于I、Q两路模拟乘法器、低通模拟器本身的不一致性、不稳定性,使I、Q通道很难达到一致,并且零漂比较大,长期稳定性不好,不能满足高性能电子战设备的要求。为此,人们提出了对中频信号直接采样,经过混频来实现正交数字下变频的方案,这种下变频的方法可以实现很高精度的正交混频,能满足高镜频抑制的要求。采用可编程器件FPGA对该算法流程进行实现,能满足在高采样率下的信号时实处理要求,在电子战领域中有着重要的意义。

1 、数字正交混频变换原理

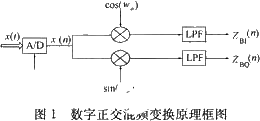

所谓数字正交混频变换实际上就是先对模拟信号x(t)通过A/D采样数宁化后形成数字化序列x(n),然后与2个正交本振序列cos(ω0n)和sin(ω0n)相乘,再通过数字低通滤波来实现,如图1所示。

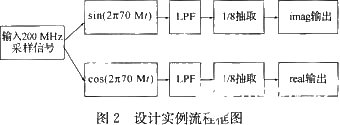

为了能够详细地阐述该算法的FPGA实现流程,本文将用一个具体的设计实例,给出2种不同的实现方法(不同的FPGA内部模块结构),比较其优劣,最后给出结论。该设计是对输入信号为中频70 MHz,带宽20 MHz的线性调频信号做数字正交混频变换,本振频率为70 MHz(即图1中的2个本振序列分别为cos(2π70Mn)和sin(2π70Mn)),将其中频搬移到0 MHz,分成实部(real)和虚部(imag)2路信号。然后对该2路信号做低通滤波,最后分别做1/8抽取输出。结构如图2所示。

根据其算法流程在MATLAB下进行仿真(低通滤波器用切比雪夫一致逼近法进行设计,过渡带为10M~45M,阶数为23),最后2路输出波形如图3所示。