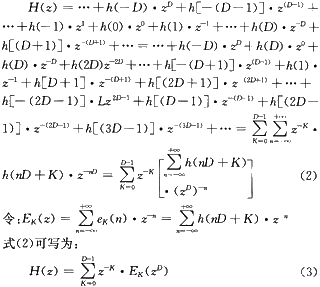

对求和式展开可重写为:

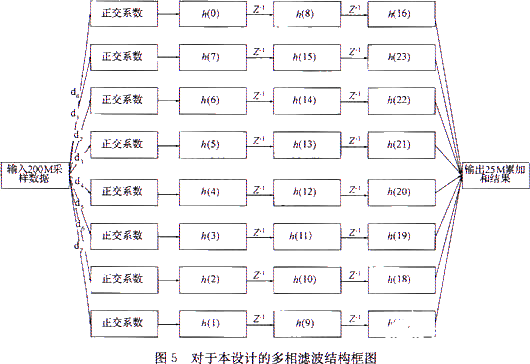

式(3)即为数字滤波器件H(z)的多相滤波结构,将其运用于抽取器,并且注意到抽取器的等效关系,则本设计FPGA内部(其中一个通道)可用图5所示的结构进行设计。

如图5所示,在200 MHz的时钟频率下,输入的采样数据以8点为周期依次打入8个通道,这样每个通道中的数据周期为200/8=25 MHz。数据进入通道后首先要乘以正交系数,在本设计中正交sin和cos表各是以20个点为一个周期,必须按照一定的等效规律将20个点排到8个通道中去,考虑到5×8=40正好是2个周期,可令N=0~39,将所对应的40个正交系数分成5组用状态机的方式打入8个通道中去,然后做乘累加。这里仍然用长度为24的滤波器,也要按照一定的规律将24个滤波系数(3个一组,见图5)排列到8个通道中去,原则是要保证在任何时刻8个通道的累加和要完全等效于原方法流程中滤波后的1/8抽取(可以验证,上面的系数排列方式是满足这一要求的)。很显然,这样做后每个通道的时钟频率都是原来频率的1/8,并且数据是完全并行处理的。乘法器和加法器都工作在25 MHz时钟频率下,可以很容易实现,且程序更加高效和科学。

4、 进一步优化的方法

采用了多相滤波方式后,每个通道需要4个乘法器。一般情况下,乘法器的延迟大概是在7~10 ns。而在25 MHz时钟频率下,完全可以将乘法器进行复用,即在40 ns周期内完成4次乘法运,算包括1次乘正交系数,3次乘滤波系数。这样每个通道只需要一个乘法器就可以。于是整个设计中所需要的乘法器可以降为16个(实部、虚部各8个),加法器则需要46个(各23个)。

5 、最终仿真波形

根据上面的多相滤波思想,并采用乘法器复用,在ISE下编写VHDL代码,用Modelsim仿真得到最终的波形,如图6所示。

用Synplify进行综合布线后得到的资源报告如下(选用的器件是VertexⅡxc2v1000):