我们前面讲过,CIC适合于窄带高倍变换领域,而这里只需要8倍变换,同时有用信号带宽是10MHz,因此采用FIR做抽取或插值滤波是更好的选择。

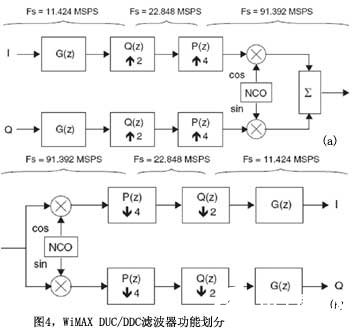

如图4所示,在功能划分时,我们考虑实现的资源和效率,将整形滤波和抽取插值滤波分为3个FIR来设计:G(z)负责频谱整形,通常是根升余弦(RRC)滤波器;Q(z)负责2倍抽取或插值滤波;P(z)负责4倍抽取或插值滤波。

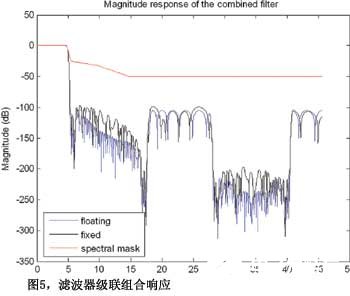

为了节省FPGA资源,提高性能,我们将工作频率最低的G(z)设计成111阶FIR,其过渡带最窄;Q(z)其次,79阶;而P(z)只有39阶,其工作频率最高。三个滤波器的组合响应如图5所示,完全满足WiMAX所要求的模板(Mask)。

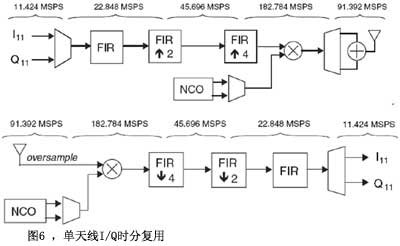

在具体FPGA实现上,我们考虑I/Q两路的滤波特性完全一致,为了节省器件资源,我们将I/Q两路的三级FIR作复用。请参考图6。

在DDC上,我们首先将91.392MSps的中频信号通过过采样(Oversample)变为182.784MSps的连续两个时钟周期的相同信号,分别和NCO混频,经过三级FIR,最终得到两路11.424MSps的I/Q信号。

在DUC上,FIR分别工作在 22.848MSps、45.696MSps和 182.784MSps。最后,将混频的两路IQ信号相加,得到一个带通的实数信号,采样率为91.392MSps。

在多通道的复用/解复用上,我们使用Altera的Avalon-ST包格式转换模块(PFC)来做模块互联。

WiMAX基站中典型的要求为2个发送天线和4个接收天线,而该参考设计也可以支持2个发送天线和4个接收天线的方式。

通过对参考设计的仿真验证,DUC的相对星座误差(Relative Constellation Error)大大好于规定值。比如,在64QAM 3/4码率时,测量的RCE为-55.29dB。DDC的接受灵敏度和邻道抑制(Adjacent Channel Rejection)指标都远好于所要求的值。

WiMAX CFR

WiMAX系统对CFR提出了更高的要求。由于采用了64QAM调制方式,误差矢量幅度(EVM)要求《3%,对峰均比(PAR)和邻频道泄漏比(ACLR)也有更严格的要求。Altera的WiMAX CFR方案采用美国乔治亚科技学院的约束钳位算法(Constrained Clipping),其EVM《3%,PAR削减》5dB,而且信号带外扩散极小。参考图7。