WiMAX DPD

WiMAX的中频带宽超过10MHz,同时需要引入LMS/RLS等自适应算法,对整个DPD模块的DSP处理能力和灵活度提出了很高的要求。采用Altera的“片内处理器NIOS II+FPGA硬件协处理单元”方式可以很好的满足设计要求。

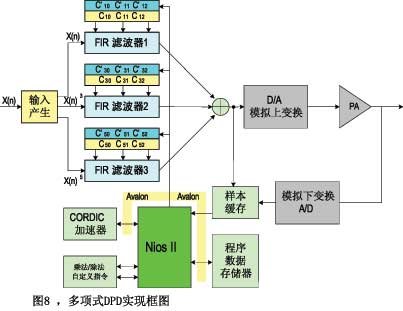

如图8所示,前向模块为预失真器,由多个FIR滤波器组成。在反向链路中,我们收集一套64个样本在“样本缓存”中,Nios嵌入式处理器可以帮助计算CORDIC的输入,CORDIC加速器完成QR分解工作。Nios然后进行倒转代换,更新前向链路中FIR滤波器的系数。采用软处理器NIOS+CORDIC加速器的方式来完成QRD_RLS的上三角矩阵运算,具有很好的灵活性,我们可以调节CORDIC加速器的数目以提高反向模块的数据吞吐率。

整个DPD参考设计的资源耗费大致为2万个逻辑单元。

TD-SCDMA

TD-SCDMA网络在国内开始大规模铺设,目前国内厂商基站的数字中频多采用大厂的专用芯片(ASSP)。对于6~8天线的应用,完成DUC/DDC/CFR/DPD等功能,可能会使用到超过10片ASSP。无论是在成本、功耗和灵活性上,都非常不理想。

Altera的TD-SCDMA数字中频方案可以在2片~3片FPGA上完成上述功能,从而在降低系统成本、功耗,提高集成度,以及可升级性上都有较大优势。

值得一提的是,目前Altera针对TD-SCDMA的CFR方案采用波峰修整算法,所需的FPGA资源较小(约3000逻辑单元+7乘法器+7块存储器),同时性能可以很好的满足3G的需求。

责任编辑:gt

关于FPGA,ASIC技术就介绍完了,您有什么想法可以联系小编。