然而,对于 FPGA 互联架构来说,仍然有着很多细节问题需要注意。例如,连线长度、互联方法、逻辑块结构,等等。这些问题往往与希望研究的主要问题无关,但都是必须统筹考虑的问题。尽管单向导线(unidirectional wires)也许是个好的想法,但如果我们将其用于所有的互联节点,那么面积和容抗的增加将迅速掩盖这个想法带来的优点和好处。那么,如果我们只将其用于 50%的互联节点,然后将所有的逻辑块输出连接到奇数号导线、将所有逻辑块输入连接到偶数号导线呢?如果我们又想到了其他的互联架构和方式呢?在这项成果面世之前,这些问题都是无法求解的。

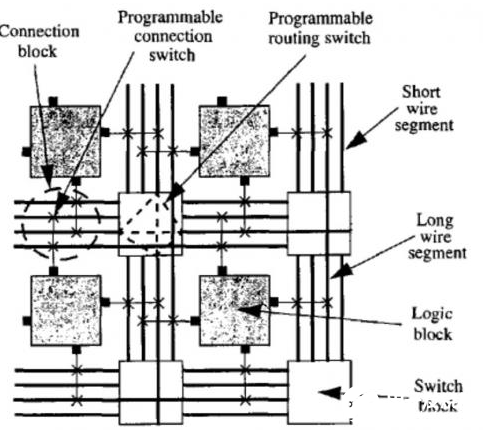

因此,解决这类问题的重点,是这项成果所展示的架构描述语言,以及 VPR 中的架构生成器。简单来说,这项成果专注于处理那些布线架构中没人关心、但却非常重要的细节问题,比如:逻辑块是如何连接的?如何保证连线之间的交互不会对系统产生不确定影响?交换架构是如何组织排列的?当设计中存在长导线时,如何保证这条穿过芯片多个区域的连线以合理的方式进行分段?……等等等等。而这项成果就是用来解决这些在 FPGA 架构研究中的细微问题。

正是如此,尽管这项工作并没有专注于架构研究的重点和流行的部分,但它极大的帮助了这个领域向前推进了一大步。通过提供更加高效的工具,这项工作使研究人员更有生产力,从而在另外一个角度帮助 FPGA 架构研究带来了大量创新。

04

时序驱动的 FPGA 布局算法

一句话总结:现代 FPGA CAD 工具中的核心布局与时序优化算法。

英文名:Timing-driven placement for FPGAs

作者:Alexander (Sandy) Marquardt, Vaughn Betz, Jonathan Rose

发表时间:2000 年

推介人:Jason Cong(加州大学洛杉矶分校)

众所周知,VPR 是 FPGA 学术界最流行的开源 CAD 软件,几乎每个新的 FPGA 架构研究都使用了 VPR。而这项成果就详细阐述了在 VPR 中使用的时序驱动的布局算法。在这项成果中介绍的 T-VPlace 算法,除了广受好评和广泛使用之外,它还对 FPGA 的布局算法有着三个重要的贡献。

第一,在 T-VPlace 算法中,时序优化的过程是通过最小化延时与导线长度的加权和实现的。这个计算过程通过一个基于模拟退火(simulated annealing)的优化引擎完成。其中,每个节点的权值是该节点时序临界性的多项式函数。这项工作的结果表明,这种权值函数能够得到很好的时序收敛。此外,导线长度和时序都可以根据前一次的迭代进行自主归一化,这使得算法有着很好的稳定性。