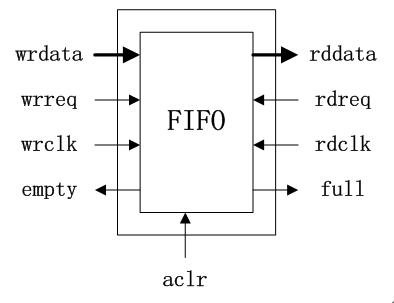

FIFO一般还会有指示内部状态的一些接口信号,如图2中的空标志位empty、满标志位full,甚至还会有用多位数据线表示的FIFO当前数据量,这些状态标志保证了读写控制不出现空读和满写的情况。清除信号aclr在某些应用中也是需要的,它在有效时能够清除当前FIFO的数据,让FIFO复位到一个空的状态。

图2 常见异步FIFO接口

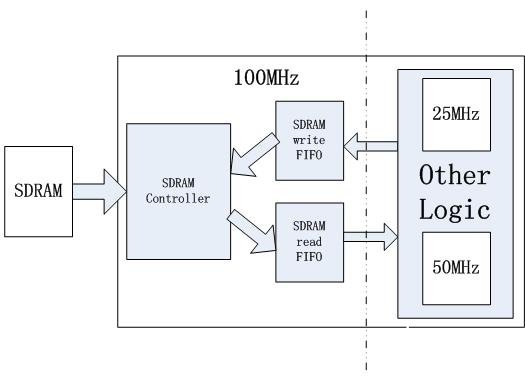

如图3所示,在特权同学设计过的一个SDRAM控制器中,就使用了两个FIFO。由于SDRAM需要定时预刷新,并且每次读写时起始控制的时间开销相对大一些,因此采用页读写的方式可以大大的提高数据吞吐量,而页读写方式需要对数据做一些缓存处理。另外,该SDRAM控制器所在的工程中涉及了多个时钟域。在写入SDRAM端是一个25MHz的时钟,在读SDRAM端是一个50MHz的时钟,而SDRAM的控制则使用了100MHz的时钟。尽管实际工程里这三个时钟的相位关系固定,但是不做好多周期约束也很容易引起问题。

最终,选择在SDRAM控制器的写入端和读出端各使用一个异步FIFO,这既解决了数据缓存的问题,也能有效的完成跨时钟域的信号传输。

图3 用两个FIFO设计的SDRAM控制器

责任编辑:gt

关于可编程逻辑就介绍完了,您有什么想法可以联系小编。