2 通用异步FIFO设计

2.1 通用异步FIFO结构

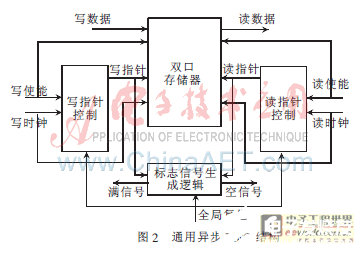

图2所示为通用异步FIFO结构,一般由四个模块构成:数据存储模块、写地址产生模块、读地址产生模块和标志位产生模块。

系统分为读时钟和写时两个完全独立的时钟域。读写两端的使能和时钟信号作为读写指针控制的基础控制输入信号。更新的读写指针既作为存储器的写入读出地址又作为标志信号模块的输入。标志产生模块通过对读写地址的比较来得到存储器的空、满标志信号。将写满信号和读空信号分别反馈到写指针和读指针控制模块,控制指针值的更新。

2.2 亚稳态消除方法

由于读写标志控制分别工作于不同的时钟域,在其产生电路中,如果比较触发器建立时间和保持时间的要求没有得到满足,触发器就会进入一个介于逻辑1和逻辑0的中间状态,称之为亚稳态。为了降低亚稳态发生的概率,可采用格雷码地址计数[3]。二进制计数器在计数值增加时,可能同时会有多位数值发生变化,而格雷码计数器每次加1只有一位数值发生变化。所以将二进制读写指针转换为格雷码,送到另一个时钟域进行比较,可以降低亚稳态发生的概率。

2.3 空、满标志产生

通过对读写格雷码地址高两位的比较,得到存储器工作的满空趋势[4],再比较地址值是否相等最终判断空、满标志。把这两个2 bit数组合成4 bit数的16种组合,可以得到:当写地址格雷码最高两位和读地址格雷码最高两位分别组合为:0001、0111、1110、1000时,存储器趋向满状态;为0100、1101、1011、0010时,存储器趋向空状态。

空、满趋势通过事件触发,随时根据读写地址的更新值进行判断。再结合读写地址的比较结果来最终判断存储器的空、满状态。

3 改进型异步FIFO设计

3.1 改进方案

根据AES/EBU音频格式可知,每192帧(384子帧)音频构成一个AES/EBU音频块,作为一个连续输出单位,并用一个Z标志来指示这一音频块的开始。根据这一标准,本文设计了一种专用于该音频格式输出的异步FIFO。该异步FIFO具有单端复位,并根据写地址复位寄存值作为读地址更新的参考,使读数据更可靠。FIFO深度设计为384子帧,位宽为24 bit。当用每个存储单元(24 bit)存储一个子帧中的音频数据码来指示地址时,由于设计深度为384子帧,利用9 bit格雷码来指示地址时,最高两位不会达到10的情况下,那么在满、空标志判断中的趋势判断就可以少考虑一种情况,即写、读地址格雷码最高两位组合为0001、0111、1100时,趋向满;为0100、1101、0011时,趋向空。这种改善,既减小了存储器的大小,又减小了程序的复杂度。