边界扫描方式需要连接计算机,无法在现场使用,嵌入式系统中很少采用这种方式。

通过上述的分析,在嵌入式系统中要使用FPGA时,可以采用专用EPC配置器件、PS、PPS、PPA和CPLD配置器件,但是PS、PPS、PPA比专用EPC配置更具成本和体积优势。在PS、PPS、PPA中,PS又是最优的通信方式。所以在嵌入式系统中,选择利用CPLD配置器件的PS被动串行方式来配置FPGA最为合适。

而本文正是利用CPLD配置控制器基于PS方式进行FPGA配置的新方法,在每次启动系统时,由配置控制器从Flash中读出FPGA配置文件的数据信息,再下载到FPGA中以完成器件的配置功能。当系统需要升级更新FPGA配置文件时,可通过网络或者由主机通过JTAG接口(未联网时)将配置文件发送给基于Nios II处理器的嵌入式系统中,由Nios II处理器更新系统中的Flash。当Flash内容更新后,系统就可实现在加电时由CPLD配置控制器自动将配置文件下载到FPGA中。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。CPLD配置控制器主要是在配置FPGA时将FLASH存放的配置文件中的并行数据转化为串行数据,实现系统的加电自运行。

3 嵌入式系统中FPGA 的配置电路设计

3.1 PS方式配置时序

在嵌入式系统中,配置控制器可以产生配置时序,能够和FPGA直接通信,将FLASH 中的配置文件传输到FPGA 的SRAM 中去。通常使用PS被动串行方式进行配置FPGA,下面就通信中使用到的5根信号线的配置时序进行说明。

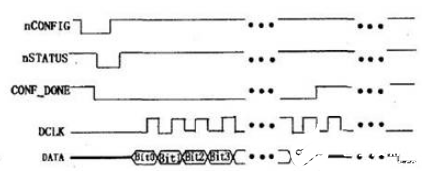

5根信号线分别为nCONFIG、nSTATUS、CONF_DONE、DCLK、DATA,连接配置控制器的5个I/O 口和对应的FPGA的引脚,配置时序图如图2所示。

图2 PS方式配置信号时序图

配置控制器上的5个I/O端口连接上述5个信号线。其中连接nCONFIG、DCLK、DATA端口设置成输出态,nSTATUS、CONF_DONE端口设置成输入态。当配置控制器开始与FPGA通信时,配置控制器首先在nCONFIG上送出一个大于8 um的负脉冲,并且检测nSTATUS 上的信号。当FPGA 接收到nCONFIG上的下降沿时,迅速将nSTATUS和CONF_DONE拉低,并且保持低电平信号一直到nCONFIG抬高电平。当nCONFIG上抬高电平后过1 um,nSTATUS也将电平抬高,配置控制器检测到nSTATUS上的变化后认为FPGA 已经做好了接收数据的准备。下一步配置控制器将产生配置时钟脉冲,配置时钟的第一个上升沿至少要比nSTATUS上升沿晚1 um。又由于配置数据和配置时钟上升沿同步,所以在配置时钟上升沿发生之前,数据线必须已经有了配置数据信号。配置数据是按照低位在前高位在后的顺序把数据送上数据线。当所有数据都传输完毕后,CONF_DONE线上电平被抬高以示配置完毕。如果传输中出现了异常,FPGA迫使nSTATUS拉低电平,配置控制器一旦检测到了这种现象将重新开始配置。由于配置文件中已经包含了FPGA初始化的一些代码,所以传输完配置文件后,FPGA就可以正常工作了。