其中△θ·n=2πf0/fc是连续两次采样之间的相位增量,控制△θ可以控制合成信号的频率。把整个周期的相位2π分割成q等份,每一份δ=2π/q为可选择的最小相位增量,得到最低频率输出fmin=δ/2πTc=fc/q,经过滤波后得到S(t)=cos(2πfct/q)。

如果每次相位的增量选择为δ的R倍,即可得到信号频率f0=Rδ/2πTc=Rfc/q,相应得到的模拟信号为S(t)=cos(2πfcR/q)。

由以上原理可知,DDS输出信号的频率与参考时钟频率及控制字之间的关系为f0=K·fc/2N,式中f0为DDS输出信号的频率,K为频率控制字,fc为参考时钟频率,N为相位累加器的位数。在波形存储器中写入2N个正弦波数据,每个数据有D位。不同的频率控制字导致相位累加器的不同相位增量,从而使波形存储器输出的正弦波的频率不同。

2 、基于DDS的跳频信号产生核心模块的设计

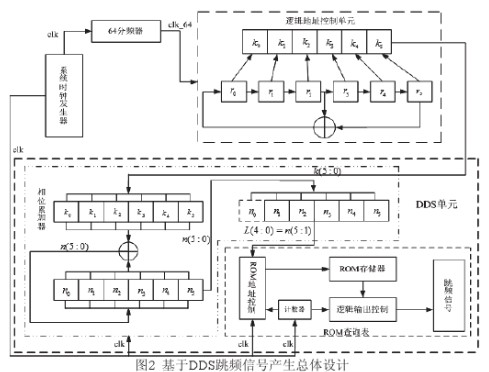

图2为基于DDS跳频信号产生的总体设计。

如图2所示,整个系统由两个部分组成,即逻辑地址控制单元和DDS单元。其中DDS单元又包括相位累加器和ROM查询表。逻辑地址控制单元用来产生不同的频率控制字,改变相位累加器的累加值。DDS单元依据频率控制字产生相应频率的信号。

2.1 逻辑地址控制单元

在本设计中,逻辑地址控制单元由一个6级移位寄存器和6位存储器构成。系统时钟clk经过64分频后得到时钟clk_64,将clk_64作为逻辑地址控制单元的驱动时钟。当一个时钟clk_64上升沿到来时,r(1:5)=r(0:4)同时。这样移位寄存器中的状态将改变,并存入存储器中,得到频率控制字k(5:0)。

2.2 DDS单元

DDS单元为本设计的核心,由相位累加器和ROM查询表两部分组成。在频率控制字(5:0)的控制下产生相应频率的信号。

2.2.1 相位累加器

相位累加器是DDS的重要的组成部分。被用来实现相位的累加,并将其累加结果存储。如果相位累加器的初值为φ0,则经过一个时钟周期后相位累加器值为φ1,即φ1=φ0+k,其中k为频率控制字。当经过n个时钟周期后φn=φ0+nk。可见φn为一等差数列。

在本文中基于FPGA的相位累加器设计如图2所示。从图2中可以看出,相位累加器由一个数字全加器和一个数字存储器构成。为了提高DDS输出频率的分辨率,一般要求n足够大,这样就要求ROM中存储大量数据。但是考虑到硬件资源有限,所以在相位累加器中采用了截短处理,这样既可保证较小的频率分辨率,又节省了硬件资源。