结合本设计中需要输出两路频率较高的本振信号,并且其中一路带宽较宽的特点,综合相位噪声、杂散抑制等因素,决定采用锁相环频率合成技术来实现该本振源。

1.1 整体框架

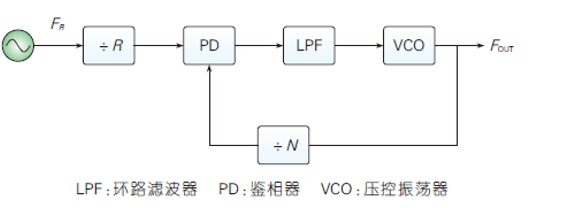

图1 是PLL 的基本结构,锁相环电路的组成部分主要包括压控振荡器(VCO)、鉴相器(PD)、环路滤波器(LPF)和分频器。

图1、PLL 结构框图

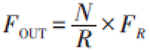

参考源给出的输入信号FR 通过R 分频器降低为鉴相器的检测频率FPD ,而VCO 的输出频率经过N 分频器后得到输入鉴相器的另一路信号FN ,两路信号通过鉴相器进行相位比较,它们产生的相位差转换为电压或电流,经过低通的环路滤波器(LPF)滤除噪声和高频分量后送入VCO 用来控制VCO 的输出频率。当锁相环稳定后,即FPD 和FN 同频同相的状态下,锁相环的输出频率为:

相位噪声是衡量本振源的重要指标,收发信机的调制与解调精度(EVM)受系统的相位噪声影响,若相位噪声过大,则系统解调出的星座图会出现旋转,因此首先要降低本振源的相位噪声。影响相位噪声的因素有很多,在近端,相位噪声主要取决于参考信号、N 分频器、鉴相器以及电源。通过式(2)可以估算出环路带宽内的相位噪声:

PN = PNfloor + 10log(N) + 10log( fvco )

在输出频率不变的情况下,降低分频比N 可以改善相位噪声。一般来说,本振系统的参考源是全球定位系统(GPS)下行的10 MHz。由于在此设计中需要较高的输出频率,为了获得良好的相位噪声,故选择提升参考频率。在整个系统前端先设计一个锁相环电路,将10 MHz 参考信号提高至100 MHz。由式(2)可知:系统的相位噪声将会降低10 dB;而在环路带宽外,相位噪声主要受VCO 影响。为了得到更好的频率稳定度和相位噪声,本设计中用100 MHz 的恒温晶体振荡器(OCXO)代替VCO。

由于两路本振信号在系统中被同时使用,为了保证信号的一致性,需要采用同一个参考源,图2 为本振源结构框图。ADI 公司的频率合成器ADF4002,结合外部恒温晶振XO5051 以及GPS 参考源10 MHz,并且组成PLL 频率合成器。该模块输出100 MHz 的信号经过集总元件组成的功分器后分成2 路,分别作为2个ADF5355 的参考频率,ADF5355 是集成VCO 的宽带频率合成器。第1路参考信号通过ADF5355 的锁相环和倍频器后输出8.4~11.2 GHz 的信号,以100 MHz 步进可调的本振信号,然后经过滤波器和放大器HMC441 得到最终所需的射频本振;第2 路100 MHz 参考信号通过另一个ADF5355 的锁相环电路并且再输出5.4 GHz 的信号,再经数字衰减器HMC425A 和放大器GVA_83+,得到所需功率的中频本振。