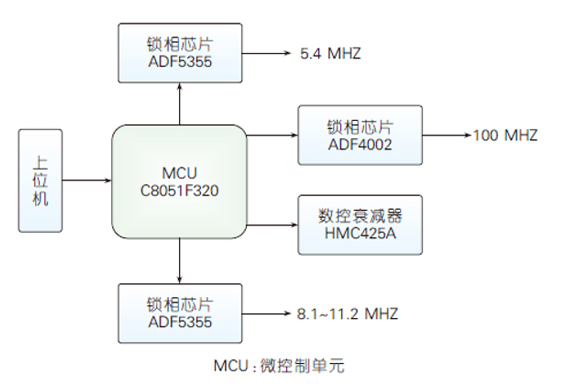

图2、本振源结构框图

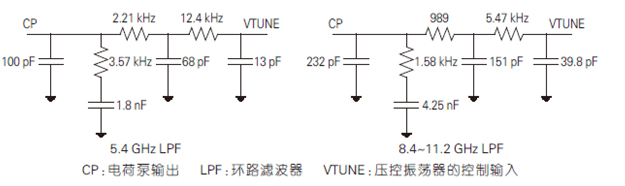

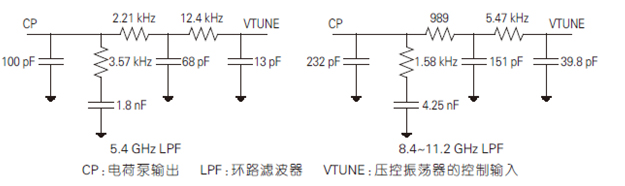

1.2 环路滤波器设计

环路滤波器是锁相环电路中的重要组成单元,它可以为VCO 提供干净稳定的调谐信号,维持环路稳定性,控制环路带内外噪声,抑制参考边带杂散干扰。环路滤波器的重要参数为环路带宽和相位裕度。环路带宽的减小可以改善杂散的抑制以及VCO 近端的相位噪声,但同时增加锁定时间,并导致远端相位噪声的恶化;而环路带宽增大则会减少锁定时间,不过无法保证VCO 近端的杂散和相位噪声抑制。此外,当环路带宽为鉴相频率的1/10 到1/5 时,锁相环会失锁[4-5]。

综合环路稳定性、杂散抑制、相位噪声、锁定时间等因素,最终确定输出频率为100 MHz 的锁相环环路带宽为30 Hz,同时输出5.4 GHz 以及8.4~11.2 GHz 的PLL 环路带宽则为100 kHz。图3 给出了两路锁相环电路中四阶滤波器的结构和取值。

图3、环路滤波器结构

1.3 单片机部分设计

本设计中采用单片机C8051F320对ADF4002、2 个ADF5355 芯片以及数控衰减器HMC425A 进行输出频率和功率的控制,其中两路ADF5355 共用数据传输和串行时钟线。图4 为单片机控制电路结构图。

图4、单片机控制电路

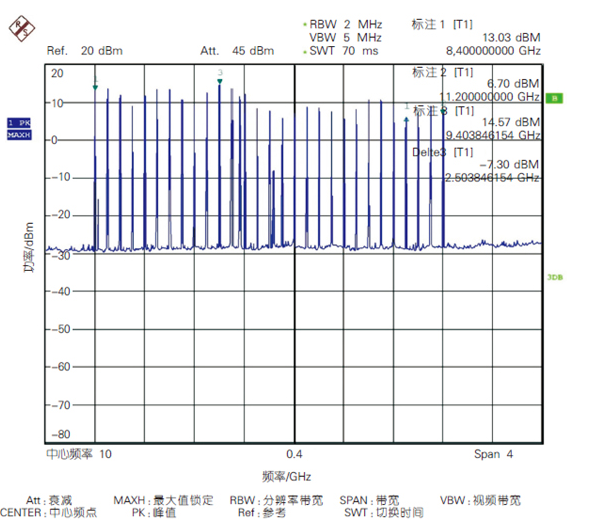

2、测试结果与实物图

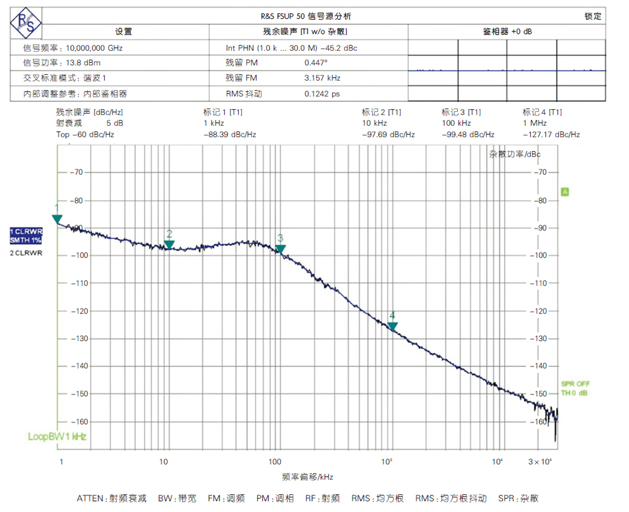

本设计实现了两路不同频率的本振信号输出,具有较好的相位噪声。利用RS 的相位噪声分析仪分别对两路输出信号的相位噪声进行了测量,结果如图5、6 所示。在8.4~11.2 GHz 频带内选择10 GHz 信号的相位噪声测试结果,参考频率源为相噪仪自带的10 MHz。

图5、ADF5355 输出5.4 GHz 相位噪声