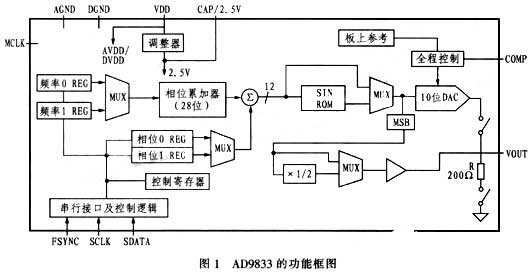

AD9833的内部电路主要有数控振荡器(NCO)、频率和相位调节器、Sine ROM、数模转换器(DAC)、电压调整器,其功能框图如图1所示。

AD933的核心是28位的相位累加器,它由加法器和相位寄存器组成,每来1个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。正弦查询表包含1个周期正弦波的数字幅度信息,每个地址对应正弦波中0°-360°范围内的1个相位点。查询表把输入的地址相位信息映射成正弦波幅度的数字量信号,去DAC输出模拟量,相位寄存器每经过228/M个MCLK时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,这样就输出了一个正弦波。输出正弦波频率为:

fOUT=M(fMCLK/228) (1)

其中,M为频率控制字,由外部编程给定,其范围为0≤M≤228-1。

VDD引脚为AD9833的模拟部分和数字部分供电,供电电压为2.3V-5.5V。AD9833内部数字电路工作电压为2.5V,其板上的电压调节器可以从VDD产生2.5V稳定电压,注意:若VDD小于等于2.7V,引脚CAP/2.5V应直接连接至VDD。

2.2 功能描述

AD9833有3根串行接口线,与SPI、QSPI、MI-CROWIRE和DSP接口标准兼容,在串口时钟SCLK的作用下,数据是以16位的方式加载到设备上,时序图如图3所示,FSYNC引脚是使能引脚,电平触发方式,低电平有效。进行串行数据传输时,FSYNC引脚必须置低,要注意FSYNC有效到SCLK下降沿的建立时间t7的最小值。FSYNC置低后,在16个SCLK的下降沿数据被送到AD9833的输入移位寄存器,在第16个SCLK的下降沿FSYNC可以被置高,但要注意在SCLK下降沿到FSYNC上升沿的数据保持时间ts的最小和最大值。当然,也可以在FSYNC为低电平的时候,连续加载多个16位数据,仅在最后一个数据的第16个SCLK的下降沿的时将FSYNC置高,最后要注意的是,写数据时SCLK时钟为高低电平脉冲,但是,在FSYNC刚开始变为低时,(即将开始写数据时),SCLK必须为高电平(注意t11这个参数)。