当AD9833初始化时,为了避免DAC产生虚假输出,RESET必须置为1(RESET不会复位频率、相位和控制寄存器),直到配置完毕,需要输出时才将RESET置为0;RESET为0后的8-9个MCLK时钟周期可在DAC的输出端观察到波形。

AD9833写入数据到输出端得到响应,中间有一定的响应时间,每次给频率或相位寄存器加载新的数据,都会有7-8个MCLK时钟周期的延时之后,输出端的波形才会产生改变,有1个MCLK时钟周期的不确定性,因为数据加载到目的寄存器时,MCLK的上升沿位置不确定。

3、 AD9833的引脚功能及时序

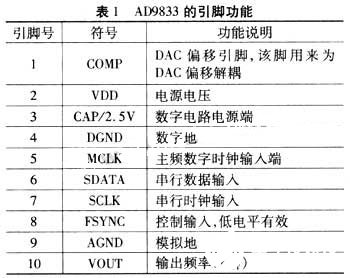

AD9833的引脚排列如图2所示,各个引脚的功能描述见表1。

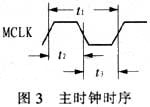

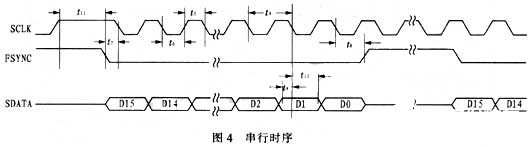

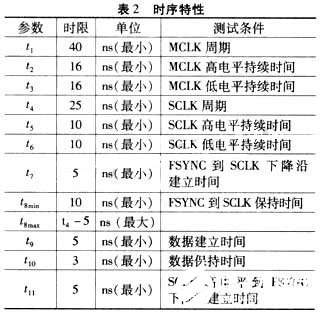

AD9833的时序特性如图3、图4和表2所示。

4、 AD9833的内部寄存器功能

AD9833内部有5个可编程寄存器,其中包括3个16位控制寄存器,2个28位频率寄存器和2个12位相位寄存器。

4.1 控制寄存器

AD9833中的16位控制寄存器供用户设置所需的功能。除模式选择位外,其他所有控制位均在内部时钟MCLK的下沿被AD9833读取并动作,表3给出控制寄存器各位的功能,要更改AD9833控制寄存器的内容,D15和D14位必须均为0。