如果模式寄存器放在Code区,则会避免这种情况。配置写模式寄存器的总线是CPU DBus(访问Code区),配置同时必然不会有读Flash(IBus/DBus访问Code区)的操作,因此下一刻即可以开始进行状态机从READ到WAIT_WR或WAIT_WR到PROG的跳转,WAIT_WR跳转到PROG后会开始Flash PROG时序转化。

3.3 Flash读操作

Flash读操作,控制器可以直接将AHB总线读操作进行Flash读时序转换。Flash控制器的READ状态和WAIT_WR状态都支持AHB总线读操作。

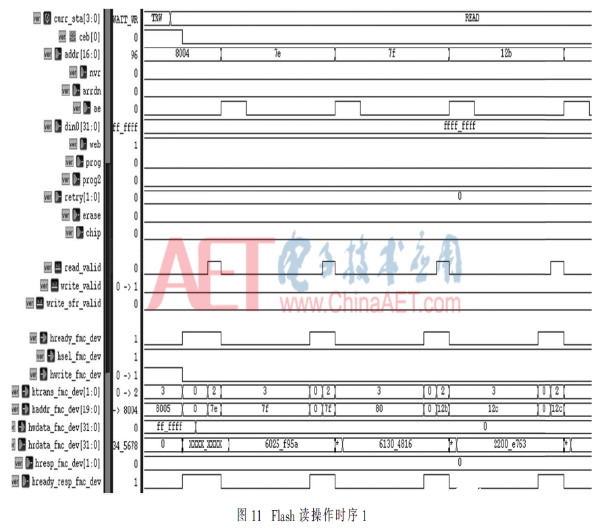

READ状态的读操作时序图如图11所示。

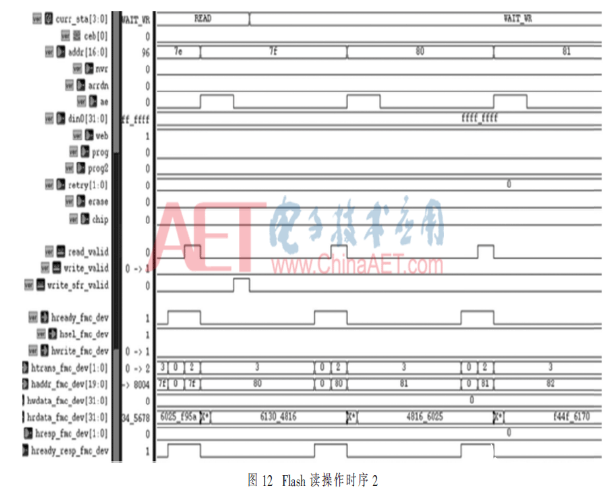

WAIT_WR状态的读操作时序图如图12所示。

3.4 Flash写操作

控制器在PROG状态可以完成Flash写操作的时序转化,采用hready拉总线方式。

进入PROG状态需要CPU执行两步总线写操作,第一步,总线配置写模式,第二步,总线写操作给出写地址,写数据的采样利用的就是AHB总线写操作的数据在扩展周期稳定的原理。

详细的Flash写操作的步骤是:

(1)配置写模式,READ状态跳转到WAIT_WR状态;

(2)在WAIT_WR状态,向目的地址发起AHB总线写,状态机跳转到PROG状态,同时锁定总线的写地址,然后利用hready拉低时数据保持的原理,锁定总线的写数据,然后进行PROG时序转化;

(3)在PROG状态,PROG信号拉高,PROG2产生写脉冲,完成word的写入。之后hready信号被释放拉高,状态机跳到TRCV_P,之后TRW,返回READ态。

注:如果在PROG状态有AHB总线读操作,hready会被拉低,读控制信号和读地址被锁存,持续到编程时间结束,直到返回READ态,正确返回读结果。

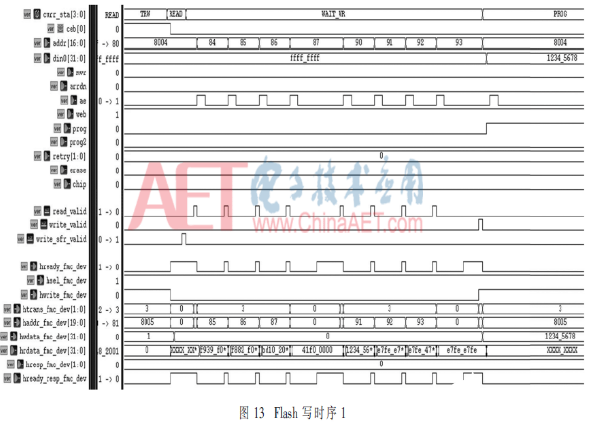

举例:以图13、图14为例说明Flash写操作时序。比如向0x00_8004地址(CPU地址0x0002_0010)写入0x1234_5678数据。write_sfr_valid信号(配置PROG模式脉冲)触发READ状态跳到WAIT_WR状态,然后write_valid信号(AHB总线写0x0002_0010地址,数据为0x1234_5678)触发WAIT_WR状态跳到PROG,开始时序转化。

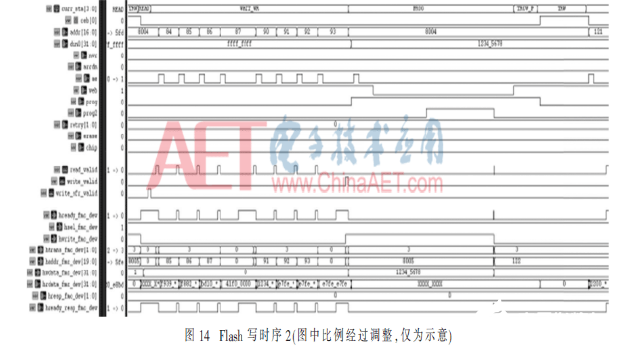

READ-》WAIT_WR-》PROG写操作时序图如图13所示。

完整的写操作PROG时序示意图如图14所示。