今天小编要和大家分享的是处理器,DSP相关信息,接下来我将从采用数字信号处理器实现软件锁相环的Z域模型搭建,鉴相器和锁相环电路制造技术这几个方面来介绍。

处理器,DSP相关技术文章采用数字信号处理器实现软件锁相环的Z域模型搭建

随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。在软件无线电接收机中采用的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)。

尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题。

1 软件锁相环的基本模型

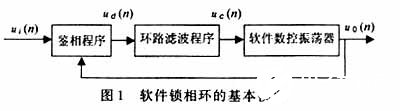

在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。

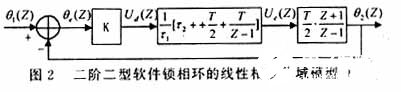

如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。

首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型。由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点,因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。

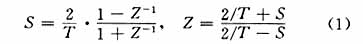

式(1)是双线性变换法的复频域表达式:

其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。