对于MEMS,微缩化是除成本和性能之外的另一个差异化要素。2007年以来,技术发展趋势是开发3D异构MEMS功能,包括通过TSV连接IC(图7)。

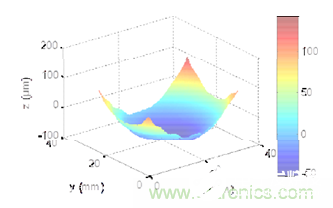

图9:使用ShadowMoiré干涉仪在室温下测量80µm硅中介层的裸片级翘曲,测量结果有一个球面非线性翘曲。

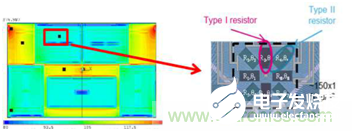

图10:中介层机械应力场模拟(左图)和8片负应变传感器放置方式(右图)。

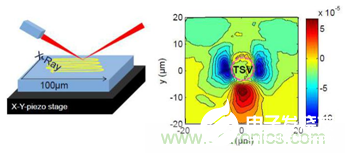

研究人员利用X射线衍射技术对TSV集成引起的局部应变进行了表征实验(图11)。同步辐射源纳米级聚焦X射线衍射测量图高亮显示了TSV周围应变的2D平面分布情况,并证明应变分布与3D FEM模拟相关。

图11:使用纳米聚焦X射线束衍射方法测量的TSV周围应变2D平面空间应变分布。稀化样品是在室温和原位退火过程中完成测量。

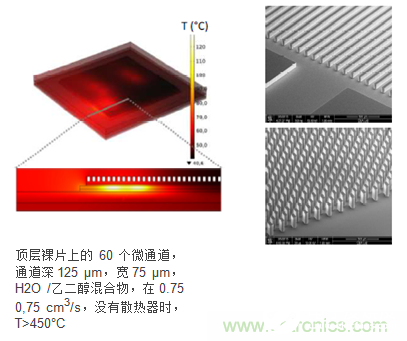

热管理是业界关注的影响3D性能的一个主要问题。精确的FEM模型和在TSV 3D电路上校准的紧凑型热模型有益于设计流程改进,研究人员做过高导热率散热器材料的评测,这种材料可以提高封装的散热性能,耐受更大的耗散功耗,可以显著降低潜在的局部热点效应(图12),高性能冷却技术被证明具有嵌入式微流体特性(图13)。

图12:3D电路被动散热器评估:顶层裸片使用铜散热器与使用热解石墨薄板(PGS)散热器的温度原位测量对比(300mW热点)。

图13左图)在一个热点密集且密闭Wioming 3D电路上的微流体冷却技术(2000W/cm²)。右图)在Si中蚀刻的微通道和鳍引脚的SEM图像

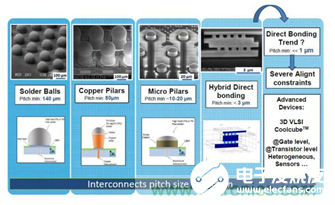

互连密度提高:混合引线键合工艺是一个前景很好的微凸点技术的替代方法,或者可以替代裸片互连使用的TSV直接氧化物键合方法(图14)。

图14:互连线间距随着新技术解决方案和机会的出现而发展变化。

混合键合工艺允许在后工序进行低节距的面对面的层叠,但也给集成和设计优化带来新挑战。

CEA-Leti发布了一个集成背面照明(BSI)与控制逻辑单元的晶圆级混合键合封装,证明低节距(5µm至24µm)焊盘对准精度在400nm以下,并使用了2x6金属层0.13µm双大马士革镶嵌工艺(图15)。