本文提出了一种延迟锁相环(Delay -locked loop DLL)的设计方案,事实上,PLL主要是利用其中的鉴相器和滤波器监测反馈时钟信号与输入时钟信号,然后用产生的电压差控制压控振荡器,从而产生一个近似于输入时钟的信号,最终达到锁频之目的,DLL的作用就是在输入时钟和反馈时钟之间插入延时脉冲,直到这两个时钟上升沿对齐,并达到同步,当输入时钟脉冲沿和反馈脉冲沿对齐后,片上延时锁相环DLL才能都被锁定。锁定时钟后,电路不再调整,两个时钟也没有什么差别,这样,片上延时锁相环就用DLL输出时钟补偿了时钟分配网络造成的时间延迟,从而有效地改善了时钟源和负载之间的时间延迟。首先,延迟线与振荡器相比,受噪声较小,这是因为波形中被损坏的过零点在延迟线的末端就消失了,而在振荡器电路中又会再循环,因而会产生更多的损坏,其次,DLL中控制电压的变化内迅速改变延迟时间,也就是说,传输函数简单地等于VCDL的增益KBCDL,总之,PLL中用到的振荡器存在着不稳定性和相位偏移的积累,因而在补偿时钟分别在网络造成时间延迟时,往往会降低PLL的性能,因此,DLL的稳定性和稳定速度等问题比PLL要好。

◇ 总体电路结构设计

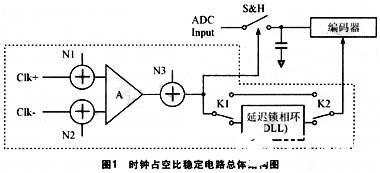

该时钟占空比稳定电路的总体结构如图1中的虚框所示,它由输入缓冲放大器A,开关K1、K2和延迟锁相环(DLL)组成。

当采样时钟频率低于DLL的工作下限时,开关K1、K2向上闭合,DLL被旁路;当开关K1、K2向下闭合时,DLL开始作用,并调节输入时钟信号相位,以使输入时钟的占空比接近50%,抖动小于0.5ps。

◇ 延迟锁相环(DLL)

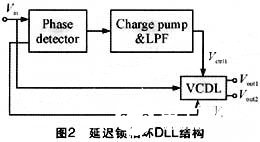

延迟锁相环(Delay-locked loop,DLL)的结构与普通锁相环(Phase-locked loop,PLL)相似,它只是用电压控制延迟线(VCDL,Voltage Control Delay Line)代替了压控振荡器。其结构框图如图2所示,一个普通的DLL包括4个主要模块:鉴相器、电荷泵电路、环路滤波器及VCDL。其中压控延迟线是由一系列电压控制的延迟可变电源串联而成的开路链,其输出信号是输入信号的延迟ntd。把压控延迟线的输入和输出送入鉴相器中进行比较,通过锁相环路使两者之相差锁定在一个周期(同相比较)或者半个周期(倒相比较),则每个延迟单元的延迟时间即为T/n或T/2n,其中n为延迟的级数。

DLL中的鉴相器的作用是鉴别相位误差并调节电荷泵的误差,以此来控制压振荡器的输出频率,常见的鉴相特性有余弦型、锯齿型与三角型,鉴相器可以分为模拟鉴相器和数字鉴相器两种,其主要指标有: