时钟占空比稳定电路

随着新时期武器装备中电子系统功能的不断扩大及性能的不断提高,电子系统的复杂程度也不断增加,为了保证电子系统的数据采样、控制反馈和数字处理的能力和性能,现代军用电子系统对A/D转换器的要求也越来越高,尤其是军事数据通讯系统,数据采集系统,对高速、高分辨率A/D转换器的需求在不断增加,时钟占空比稳定电路作为高速、高精度A/D转换器的核心单元,对转换器的信噪比(SNR)和有效位(ENOB)等性能起至关重要的作用,因此要保证高速、高精度A/D转换器的性能,必须首先保证采样编码时钟具有合适的占空比和很小的抖动,因此,开展时钟占空比稳定电路的研究十分需要。

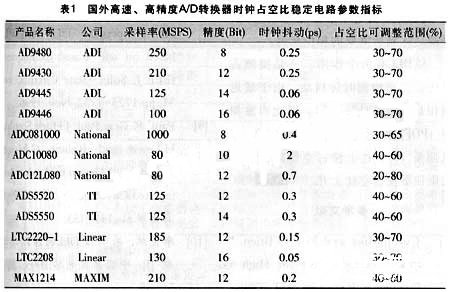

由于时钟占空比稳定电路是高速、高精度A/D转换器的核心单元,而单独的时钟占空比稳定电路产品几乎没有,只有在高速、高精度A/D转换器中才有报道,ADI公司产品与其他公司产品相比之所以能提高采样性能,主要得益于对DCS(duty cycle stabilizer)电路的改进,DCS电路负担着减小时钟信号抖动的作用,而采样时序就取决于时钟信号,各家公司过去的DCS电路只能将抖动控制在0.25ps左右,而高性能新产品AD9446和LTC2208则可将抖动降低到50fs左右,通常降低抖动就能够改善SNR,从而提高有效分辨率(ENOB:有效比特数),并在达到16比特量子化位数的同时,能实现100Msps以上的采样速率,如果不控制抖动就提高采样速率,则会降低ENOB,且无法获得希望的分辨率,也无法提高量子化位数,DCS电路随着高性能A/D转换器的发展,可向更高速度,更小抖动和稳定方向发展,表1所列为国外A/D转换器中时钟占空比稳定电路的主要技术和参数指标。

事实上,至今为止,AD公司的60fs的抖动已经是最小的了,现在孔径抖动一般控制在1个ps左右,高于这个数甚至高达几十个ps的抖动实际上已经没有多大的意义了。

时钟稳定电路的实现方法

从目前国内外研究的情况看,用于稳定高速ADC的时钟电路主要是锁相环路(Phase-locked loop,PLL)。锁相系统在本质上讲是一个闭环相位控制系统,简单得讲,它是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,振荡器输出信号与输入信号之间的相差为零或保持常数,由于锁相环路具有许多优良特性,故可广泛用于高性能处理器的时钟产生以及分布、系统的频率合成与变换、自动频率调谐跟踪、数字通信中的位同步提取、锁相、锁相倍频与分频等。