今天小编要和大家分享的是模拟技术相关信息,接下来我将从采用电荷定标型结构实现12bitADC的设计和仿真,12位逐次逼近寄存器型adc转换器设计这几个方面来介绍。

模拟技术相关技术文章采用电荷定标型结构实现12bitADC的设计和仿真

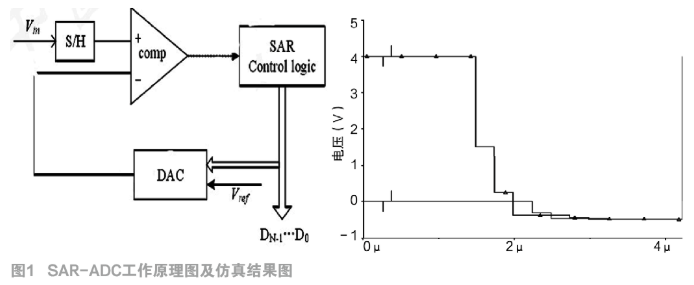

1、 SAR-ADC工作原理

逐次逼近转换器(SAR-ADC)由采样保持、比较器、DAC和数字控制逻辑组成,其工作原理图如图1所示。而数字控制逻辑由逐次逼近寄存器(SAR)和控制逻辑组成。其具体工作过程如下:

●模拟输入先经过采样保持送到比较器的一端,转换开始时,数字控制逻辑将逐次逼近寄存器(SAR)的最高位(MSB)置为1,其余位为0。

●DAC在SAR和控制逻辑的控制下,将Vin《Vref,送入到比较器的另一端, 此时Vin和1/2Vref进行,如果Vin》1/2Vref,比较器输出1,则SAR最高位为1,如果Vin《1/2Vref,比较器输出0,SAR最高位输出0。

●以此类推确定到SAR的最低位,完成N位数字码的确定,此时得到的数字量即为模拟输入的二进制代码。

2 、12bitSAR-ADC的设计与仿真

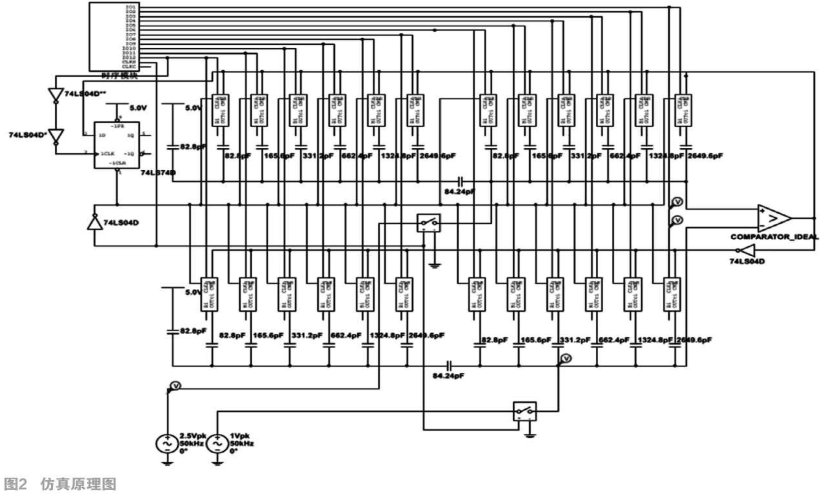

2.1原理设计说明

该设计的12bitADC具有低功耗和高精度的特点。它的原理图如图2。全差分的输入信号经采样开关和电荷定标型DAC阵列后,输入到比较器的两端。比较器的结果输入到SAR控制逻辑(即DAC电平切变电路),SAR控制逻辑可以根据比较器的结果来控制电容DAC阵列的电平切换开关,使DAC阵列的电荷重新分派。因此比较器的输入发生变化,然后在下一个时钟的低电平进行比较,并继续将比较结果送入SAR控制逻辑,之后不断重复。在12个比较周期后,可由SAR的输出得到12位数字结果。此时系统复位,等待下一次比较。

电路图左上角是时序产生电路,由此为ADC提供采样时钟,比较时钟;中间部分是SAR控制逻辑(即DAC电平切变电路)和电容DAC阵列;最右边是理想比较器;左下方是差分输入的正弦信号。

由图中可见,差分输入的正弦信号经采样开关输入到电容DAC阵列中和理想比较器的两端。之后比较器的输出输入到SAR控制逻辑从而控制DAC阵列的电平切换,使比较器的输入发生变化。而数字结果可由SAR控制逻辑输出。