SAR ADC电路的缺点是转换位数较高时,精度容易不足。因此针对12bit的ADC,我们对时序产生电路和SAR DAC模块电路部分进行了创新型设计,从而来提高ADC的转换精度,具体的设计细节将在下面的各电路模块设计予以介绍。

2.2各模块设计说明

2.2.1控制时钟产生电路

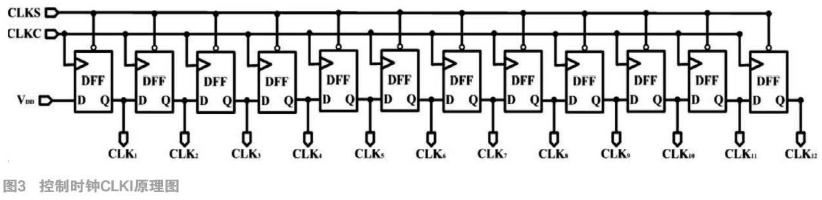

如图3所示,控制时钟产生电路由采样时钟CLKS和比较时钟CLKC以及12位移位寄存器级联而成。CLKI的产生原理为:

●当CLKS为1时,CLKC、各CLKi信号均置0,此时系统工作在采样/保持阶段;

●CLKS为0时,此时系统工作在比较阶段,产生12周期CLKC信号,并由CLKC控制移位寄存器的信号传递(上升沿触发),从而产生CLK1-CLK12的控制时钟。

2.2.2DAC电平切变控制电路

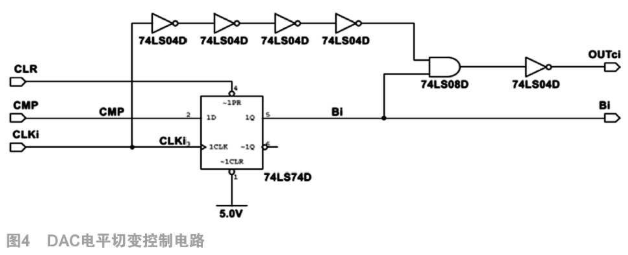

DAC电平切变控制电路主要功能是根据比较器的输出结果来控制电容阵列的电平变换。为了更好的实现差值电平的折半比较,本设计采用图4所示的电路结构。

2.2.3电容阵列

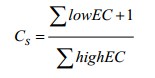

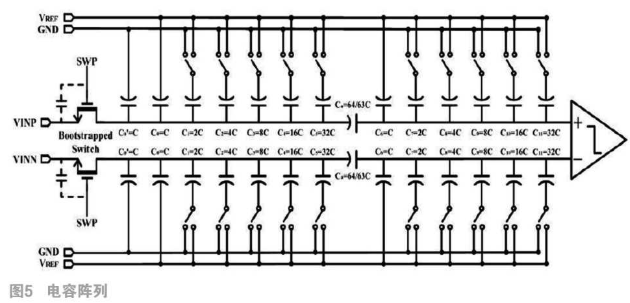

为了实现逐次逼近ADC的低功耗DAC,我们选用了电荷定标型结构,同时采用并行二进制加权电容阵结构。考虑到本设计所做的是12bitADC,那么12位DAC就需要4096个单位电容,会占用较大芯片面积同时导致转换速度降低。为了解决上述问题,DAC采用分段电容阵列结构。如图5所示,考虑到桥接电容两端的二进制加权电容阵列位数相等时,整个逐次逼近的ADC总电容最小。因此在高6位与低6位之间用一个桥接电容Cs分隔,同时低四位二进制加权电容阵列还会接一个与单位电容等值的C。采用该种设计可以将电容的数量从4096减少到约128个。因此ADC的速度更快,功耗更小,芯片面积也更小。关于单位电容C的选取,本设计综合考虑减小功耗和抑制噪声的影响,选择单位电容的容值为82.8pf。桥接电容Cs

计算可得Cs=84.11pf。综合考虑到AD转换的精确度和累计误差,桥接电容的容值为84.24pf。

2.2.4单端输入转差分输入模块

考虑到所设计的ADC是差分输入,而一般信号都单端输入形式。因此在电路中附加了单端输入转差分输入模块AD8476,以保证差分信号同相以及充分抑制共模信号,如图6。